Multimedia in Technical Teaching

(Marco Nordmann, Tamer Çatalkaya)

The production of multimedia content is very time consuming, expensive, and often overextending for technical institutions. Therefore, a long-term objective of scientific research must be the simplification of this process by minimizing the involved time and the needed multimedia competencies.

For a faster and cost-efficient production of learning programs, we developed a special reference model that is constantly being improved. It simplifies the integration of multimedia contents produced by different authoring tools into a standard-compliant online or offline learning program. If furthermore serves as a framework providing fundamental functionality and a consistent look and feel inside of the learning program. This reduces production time significantly.

The Department of Integrated Circuit Design supplements classical teaching with readings, exercises and labs by multimedia, CBT (Computer Based Training) etc. from 1996 to 2010. We successfully conducted several practical courses, seminars, study projects and diploma theses. Experiments have shown that learning using CBT is more time efficient, but for social and emotional reasons the students do not want to disclaim conventional lecturing and a script. Therefore, blended learning will enhance conventional lecturing by integrating efficient elearning methods and multimedia technologies.

The Department of Integrated Circuit Design offered a lecture called elearning. In this lecture, elearning methods were used for teaching elearning competencies.

The LAS Project: A Reference Model for developing SCORM compatible CBT and WBT

- today CBT and WBT production is restricted to the use of a single authoring tool

- the decision whether to publish as CBT or WBT usually comes with specific constraints and corresponding adjustments

- when a WBT is published, it should be SCORM compatible so it can be used on many typical learning platforms

- our project Learning Application Suite (LAS) has the goal to solve these problems

- The LA-Builder combines many Reusable Learning Objects (RLO) produced by different authoring tools, together into one CBT or WBT. It generates all the SCORM conditioned XML structures (SCORM 1.0 or SCORM 2004), creates a hierarchical structure of the used resource files, and enables the export as ZIP-compressed content package

- The LA-Player is able to play any SCORM compatible Learning application offline. It offers consistent user navigation and some extra functions like glossary, text search, tooltips, personalization, history and bookmarks etc.

- The Automatic Update enables the LAS to update not only the LAS itself, but also all installed learning programs. In order to do that, it connects to a server on the internet that keeps the current program versions and then asks the user to download and install all files that have been changed.

- The Plug-in Integration and Installation is a versatile component of the LAS. It integrates into the LA-Builder and enables the author of a learning program to check his learning application for necessary browser plug-in and then offers to download and integrate these into the SCORM package. This makes sure that the LA-player can play the SCORM package even if needed plug-in cannot be downloaded. Before the LA-player starts a learning program, the plug-in integration and installation checks, if the operating system has all the needed plug-in installed. If a plug-in is missing for proper execution of the learning program, it offers the learner to download it or to extract it from the SCORM package.

Figure 1: Designflow of the production and execution of SCORM compatible learning programs, using the LAS

Currently we are developing support of the newest SCORM 2004 standard which contains sequencing and navigation rules in order to make the learning path non-linear depending on interactions, test results or tracking information.

Computer-based Training in Chip- und System Design

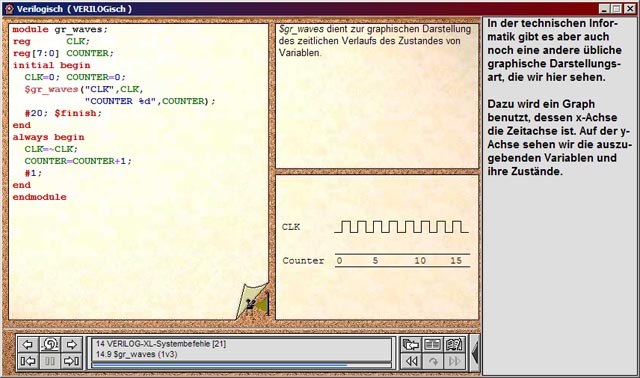

- the CBT Verilogisch integrates a real VERILOG simulator, teaching the hardware description language VERILOG used in chip design

- the CBT LogiSyn teaches the important logic synthesis in detail

- other CBTs cover fundamental concepts like parallelism and time, modular and hierarchical conception or behavior and structure

Figure 2: The CBT VERILOGgisch

Figure 3: The CBT LogiSyn

Here are some example CBTs (german only):

CBT Bildschirm-Controller A (20,5 MB, Zip)

CBT Bildschirm-Controller B (15,3 MB, Zip)

CBT Testschaltung BILBO (10,5 MB, Zip)

CBT Logiksynthese (25,5 MB, Zip)

CBT Statecharts (18,9 MB, Zip)

CBT Parallelität und Zeit (27,3 MB, Zip)

E-Learning Academic Network Niedersachsen (ELAN)

(Tamer Çatalkaya)

Von 2002 bis 2004 wurde der erste Teil des Projekts E-Learning Academic Network Niedersachsen (ELAN) durchgeführt. Das Hauptziel dieser Kooperation zwischen der Universität Hannover, der Technischen Universität Braunschweig und der Medizinischen Hochschule Hannover sowie dem Learning Lab Lower Saxony (L3S) besteht in der nachhaltigen und wirtschaftlich tragfähigen Entwicklung von eLearning-Services und -Angeboten in Niedersachsen.

Das Konzept beruht auf einem Kompetenz- und einem Inhaltsbereich. Während sich der Kompetenzbereich um den Aufbau einer Infrastruktur kümmert, übernimmt der Inhaltsbereich die Entwicklung von thematisch breitgefächerten, qualitativ hochwertigen und stark nachgefragten Inhalten.

Die Abteilung E.I.S. nahm am ELAN-Projekt im Inhaltsbereichs 1 zur Informatik, Informationstechnik und Elektrotechnik teil. Das Projekt wurde wie beantragt erfolgreich durchgeführt. Das universelle Referenzmodell für den zeit- und kostengünstigen Entwurf komplexer Lernmodule mit Sprache unter Authorware liegt als Prototyp vor. Es wurde praktisch erprobt, weiter entwickelt und gepflegt. Es wurde allen ELAN-Teilnehmern kostenlos angeboten. Die Ergebnisse werden auch im Rahmen von ELANs Best-Practice vorgestellt. Das Referenzmodell wurde angewendet bei der Entwicklung einer interaktiven multimedialen Lernumgebung mit gesprochenen Kommentaren für die Hardware-Beschreibungssprache VERILOG und ihre Synthese im Chip- und Hardware-Entwurf. Zwei Prototypen zur Hardware-Beschreibungssprache VERILOG und zur Chip-Synthese konnten vorzeitig fertig gestellt werden.

Die VeriBox

(Tamer Çatalkaya)

Hardware-Beschreibungssprachen stehen im Zentrum des Schaltungsentwurfs. Zu der von uns eingesetzten Sprache VERILOG werden grundlegenden Phänomene in der Vorlesung erarbeitet, während der praktische Einsatz in den Übungen und im Praktikum trainiert wird. Mit der VeriBox entsteht ein umfassendes multimediales Lernsystem zur Hardware-Beschreibungssprache VERILOG. Das multimediale Lernsystem VeriBox soll das Erlernen von VERILOG in Vorlesung und Übung effizienter und attraktiver machen und auch das Selbststudium fördern.

Wie auch im realen Entwurf ist die Bedeutung der Logiksynthese in der VeriBox besonders hervorgehoben. Feinheiten der Logiksynthese können die Güte der Schaltung entscheidend beeinflussen. Mit multimedialen Darstellungen können wir komplexe und dynamische Vorgänge besonders anschaulich vermitteln (Bild 6).

Bild 6: Zeitkontrollen multimedial animiert

Die Lernumgebung der VeriBox umfasst die Bereiche Einführung, grundlegende Konzepte, Beispiele und Aufgaben, Logiksynthese und Lexikon. Interaktivität steht im Vordergrund der VeriBox.

In der Einführung wird zunächst ein allgemeiner Überblick über den Einsatz von Hardware-Beschreibungssprachen gegeben und auf Unterschiede und Gemeinsamkeiten zu konventionellen Programmiersprachen hingewiesen. Ein erstes aussagekräftiges Vorab-Beispiel vermittelt dem erfahrenen Programmierer bereits eine Menge intuitiver Vorstellungen.

In den grundlegenden Konzepten werden wichtige und schwierige Phänomene vermittelt wie Parallelität und Zeit, Modularisierung und Hierarchie, Mixed-Mode-Darstellung, Verhalten und Struktur.

Der eigenständige Teil Logiksynthese unterscheidet zwischen synthetisierbaren und nicht synthetisierbaren VERILOG-Konstrukten. Er geht auf die Auswirkung von Modellierungsstilen auf das Syntheseergebnis ein und vermittelt einen Einblick in die Arbeit mit dem Design-Compiler von Synopsys.

Ein weiteres Ziel ist es, das CBT-Programm mit den professionellen CAD-Tools zum Chip-Entwurf zu koppeln. Das Lernprogramm soll also nicht nur selbständig arbeiten, sondern auch als Hilfe beim Umgang mit den CAD-Werkzeugen eingesetzt werden.

Eine typische Anwendung ist eine Fragestellung vom Lernprogramm, die nur mit dem Einsatz eines VERILOG-Simulators gelöst werden kann. Das ausgewertete Simulationsergebnis wird dann als Antwort in das Lernprogramm eingegeben.

Unsere Erfahrung hat gezeigt, dass multimediale Lernprogramme die klassische Lehre ergänzen und attraktiver machen (Blended Learning). Diese Beobachtung wurde in mehreren Feldtests belegt.

Demo zur VeriBox (5,5 MB, Zip)

Feldtest zur Logiksynthese: ein Experiment zum Einsatz von Lernprogrammen

(Tamer Çatalkaya)

Wir untersuchen die studentische Akzeptanz von Lernprogrammen und die Effizienz und Auswirkung auf das Lernen. Dazu haben wir das Kapitel Logiksynthese als Teil der Vorlesung Einführung in den Chip- und System-Entwurf für die Studie ausgewählt. Hierzu wurde das Lernprogramm LogiSyn implementiert (Bild 7). Es enthält den multimedial aufbereiteten Vorlesungsstoff. Lernprogramm und Vorlesung werden durch separat betreute Rechnerübungen ergänzt.

Bild 7: Synthese-Ablauf mit auswählbaren Komponenten

Insgesamt 63 Teilnehmer wurden zum Thema Logiksynthese zufällig in drei Klassen eingeteilt. Klasse A bekam das Vorlesungsskript und das Lernprogramm. Klasse B bekam nur das Skript. Beide Klassen A und B haben auch an der Vorlesung im Hörsaal teilgenommen. Klasse C dagegen hat ohne Vorlesung nur mit dem Lernprogramm gearbeitet. Die Klassen durften kein Wissen oder Material austauschen. Alle Teilnehmer wurden gebeten, die Arbeitszeiten und die Methode (Skript, Lernprogramm, Vorlesung) genau zu protokollieren (Bild 8).

Das gelernte Wissen wurde in einer 25-minütigen Klausur erfasst. Hierzu wurde vorgegeben, dass die Studenten sich wie zu einer Diplomprüfung vorbereiten sollten. Das gesamte Experiment war freiwillig und anonym. Die tatsächliche Vorbereitungszeit wurde in die Auswertung einbezogen.

Bild 8: Lerneffizienz