## Regular Datapaths on Field-Programmable Gate Arrays

Vom Fachbereich für Mathematik und Informatik der Technischen Universität Braunschweig

#### genehmigte Dissertation

zur Erlangung des Grades eines Doktor-Ingenieurs (Dr.-Ing.)

von

Dipl.-Inform. Andreas Koch

Eingereicht am 09.07.1997 1. Referent: Prof. Ulrich Golze 2. Referent: Prof. Rolf Ernst Mündliche Prüfung am 02.09.1997 For Anja.

### Abstract

Field-Programmable Gate Arrays (FPGAs) are a recent kind of programmable logic device. They allow the implementation of integrated digital electronic circuits without requiring the complex optical, chemical and mechanical processes used in a conventional chip fabrication. FPGAs can be embedded in traditional system designflows to perform prototyping and emulation tasks. In addition, they also enable novel applications such as configurable computers with hardware dynamically adaptable to a specific problem.

The growing chip capacity now allows even the implementation of CPUs and DSPs on single FPGAs. However, current design automation tools trace their roots to times of very limited FPGA sizes, and are primarily optimized for the implementation of random glue logic. The wide datapaths common to CPUs and DSPs are only processed with reduced performance.

This thesis presents Structured Design Implementation (SDI), a suite of specialized tools coordinated by a common strategy, which aims to efficiently map even larger regular datapaths to FPGAs. In all steps, regularity is preserved whenever possible, or restored after disruptive operations were required.

The circuits are composed from parametrizable modules providing a variety of logical, arithmetical and storage functions. For each module, multiple target FPGA-specific implementation alternatives may be generated in both gate-level netlist and layout views.

A floorplanner based on a genetic algorithm is then used to simultaneously choose an actual implementation from the set of alternatives for each module, and to arrange the selected module implementations in a linear placement. The floorplanning operation optimizes for short routing delays, high routability, and fit into the target FPGA.

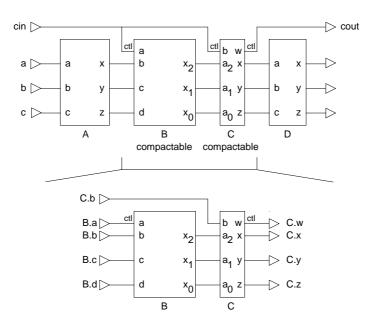

In addition, the coarse granularity of an FPGA as compared to a gate array (large logic blocks instead of small transistors as building blocks) necessitates a compaction phase to avoid inefficiencies. Floorplanning takes this into account by grouping modules amenable to compaction, and prepares for a merging of their functions across module boundaries.

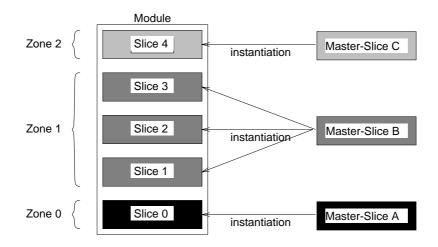

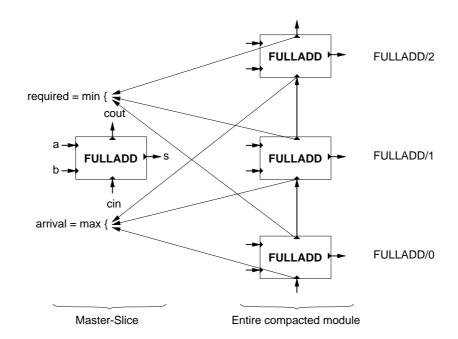

For each set of compactable modules, structure extraction and regularity analysis phases search for a common regular bit-sliced structure across all modules in the set. The new master-slices thus discovered are then processed using conventional logic synthesis and technology mapping techniques, reducing both area and delay over their pre-compaction levels.

Since the originally generated module layout is invalidated by the com-

paction operation, the mapped logic blocks in each compacted master-slice have to be re-placed in a regular manner. This microplacement operation is performance-driven, and optimizes delay, control signal routing and slice abutment across master-slice boundaries. The compacted modules are then reassembled from the microplaced master-slices according to the structural information extracted previously.

The result is the efficient mapping of a regular bit-sliced datapath architecture to a regular bit-sliced layout. Practical experiments show delay reductions of up to 33% as compared to layouts produced by conventional tools. The exploitation of regularity during processing also reduces CAD runtimes by up to 78%.

## Kurzfassung

Field-Programmable Gate-Arrays (FPGAs) sind eine noch junge Art von programmierbaren Logikbausteinen. Sie erlauben die Implementierung von integrierten Digitalschaltungen ohne die komplizierten optischen, chemischen und mechanischen Prozesse, die normalerweise für die Chipfertigung erforderlich sind. FPGAs können im Rahmen konventioneller Entwurfsmethoden zu Emulationszwecken und Prototyp-Aufbauten herangezogen werden. Sie erlauben aber auch völlig neue Anwendungen wie rekonfigurierbare Computer, deren Hardware dynamisch an ein spezielles Problem angepaßt werden kann.

Die gewachsene Chip-Kapazität erlaubt nun sogar die Implementierung von CPUs und digitalen Signalprozessoren (DSPs) auf einem einzelnen FPGA. Die Leistungsfähigkeit der entstandenen Schaltungen wird jedoch durch die zur Zeit erhältlichen CAD-Werkzeuge limitiert, da diese noch auf stark beschränkte FPGA-Größen ausgerichtet sind und primär der platzsparenden Verarbeitung unregelmäßiger Logik dienen. Die breiten Datenpfade in Bit-Slice-Struktur, die den Kern vieler CPUs und DSPs darstellen, werden nur suboptimal behandelt.

Diese Arbeit stellt Structured Design Implementation (SDI) vor, ein System von spezialisierten CAD-Werkzeugen, die auch größere reguläre Datenpfade effizient auf FPGAs abbilden. In allen Verarbeitungsschritten wird dabei die bestehende Regularität soweit wie möglich erhalten oder nach regularitätsvernichtenden Operationen wiederhergestellt.

Zur Schaltungseingabe steht eine Bibliothek von allgemeinen Modulen aus den Bereichen Logik, Arithmetik und Speicherung bereit. Diese können durch Belegung verschiedener Parameter wie Bit-Breiten und Datentypen an aktuelle Anforderungen angepaßt werden. Für jedes der Module können unterschiedliche Implementierungsalternativen in Form von Gatternetzlisten oder Layouts generiert werden.

Ein Floorplanner, basierend auf einem genetischen Algorithmus, wählt anschließend, bei gleichzeitiger linearer Plazierung der Module, für jedes Modul die günstigste Alternative aus. Dabei wird in Hinsicht auf kurze Leitungsverzögerung, gute Verdrahtbarkeit und Einpassung in das Ziel-FPGA optimiert.

Die grobe Granularität von FPGAs im Vergleich zu konventionellen Gate-Arrays (große Logikblöcke statt feiner Transistoren) erfordert eine Kompaktierung, um Ineffizienzen zu vermeiden. Dazu werden während des Floorplanning geeignete Module zusammen plaziert und die Verschmelzung ihrer Funktionen über Modulgrenzen hinweg vorbereitet. Aus jeder Gruppe von zu verschmelzenden Modulen wird nun eine modulübergreifende reguläre Bit-Slice-Struktur extrahiert und diese auf Regularitäten hin untersucht. Die auf diese Weise bestimmten neuen Master-Slices werden anschließend mittels konventioneller Logiksynthese- und Technologieabbildungsverfahren in Bezug auf Flächenbedarf und Verzögerungszeit optimiert.

Da diese Operationen das ursprünglich generierte Layout ungültig machen, müssen die Logikblöcke in den optimierten Master-Slices wieder neu plaziert werden. Diese Mikroplazierung zielt auf die Wiederherstellung eines regulären Layouts hin und optimiert dabei die Signalverzögerungen, die Verdrahtung von Slice-übergreifenden Steuerleitungen und die Anreihbarkeit der Slices. Die kompaktierten Module werden dann entsprechend der vorher extrahierten Struktur aus den mikroplazierten Master-Slices neu aufgebaut.

Das Ergebnis dieser Vorgehensweise ist die effiziente Abbildung eines regulären Datenpfades auf ein reguläres Layout unter Erhaltung der Bit-Slice-Struktur. Praktische Experimente haben eine Verminderung der Schaltungsverzögerung um bis zu 33% im Vergleich zu konventionell berechneten Lösungen ergeben. Die konsequente Ausnutzung der Regularität führt auch zu einer Verkürzung der CAD-Rechenzeiten um bis zu 78%.

### Acknowledgments

I would like to thank my thesis advisor Prof. Ulrich Golze, known to me since my first semester at Braunschweig, for many fruitful discussions, and giving me the freedom to explore and develop a broad range of CAD techniques. He also provided the hard- and software infrastructure indispensable for the success of my work.

Furthermore, I am grateful to Prof. Rolf Ernst for acting as a co-referee for this thesis.

The legibility of the text was markedly improved by considering the comments offered by Andrea Gondring and Ulf Bahrenfuss.

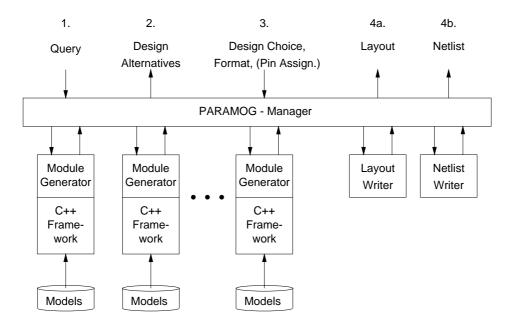

PARAMOG was made possible by the efforts of Holger Sadewasser and Jens Dittmer. It was their perseverance in reverse-engineering the XC4000 FPGA that allowed the exploitation of highly chip-specific structures during module generation.

The implementation of my SDI tool set was enabled by the free access to high-quality tools from other institutions. The well-documented and robust UCB SIS was used as framework for integrating my own functionality, as well as for providing logic optimization and technology mapping operations. For further experiments, Jason Cong (FlowMap) and Klaus Eckl (TOS-TUM) made their technology mapping tools available. Peter Barth supplied the OPBDP solver used as a first step of the hybrid ILP solving approach.

I am indebted to my parents for laying the groundwork that allowed me to successfully complete this and many of the other endeavors I have undertaken thus far.

The moral support by Anja Teske proved to be invaluable in the hectic final phase of this thesis' gestation.

# Contents

| 1 | Intro             | oductio        | n                                    | 1               |

|---|-------------------|----------------|--------------------------------------|-----------------|

| 2 | <b>Ove</b><br>2.1 |                | of Structured Design Implementation  | <b>11</b><br>12 |

|   | 2.1               |                | XC4000 FPGAs                         | 12 $12$         |

|   |                   | 2.1.1<br>2.1.2 | Logic Block Architecture             | 12              |

|   | 2.2               |                | Routing Architecture                 | 14 $17$         |

|   | $\frac{2.2}{2.3}$ |                | tured Design Entry                   | 19              |

|   | 2.3               | 2.3.1          | t Topology                           | 19<br>19        |

|   |                   | 2.3.1<br>2.3.2 | <b>I</b> 80                          | 19<br>24        |

|   | 2.4               |                | Chip Topology                        | 24<br>26        |

|   | $\frac{2.4}{2.5}$ |                | le Selection and Floorplanning       | 20<br>28        |

|   | $\frac{2.5}{2.6}$ |                |                                      | 20<br>29        |

|   | 2.0               | 2.6.1          |                                      | $\frac{29}{31}$ |

|   |                   | 2.6.1          | Soft- and Hard-macros                | 31              |

|   |                   | 2.6.2          | Preserving Module Placement          | 32              |

|   |                   | 2.6.3<br>2.6.4 | Extracting and Exploiting Regularity | 33              |

|   |                   | 2.0.4<br>2.6.5 | Logic Optimization and Mapping       | 35              |

|   | 2.7               |                | placement                            | 35              |

|   | 2.1               | 2.7.1          | Congestion Handling                  | 36              |

|   |                   | 2.7.1<br>2.7.2 | Pre-placement Activities             | 36              |

|   |                   | 2.7.2<br>2.7.3 | Regularizing Logic Blocks            | 38              |

|   |                   | 2.7.3<br>2.7.4 | Two-Phase Placement                  | 40              |

|   | 2.8               |                | n Integration                        | 45              |

| 3 | Ma                |                | enerators and Library                | 47              |

| 5 | 3.1               |                |                                      | <b>4</b> 7      |

|   | 0.1               | 3.1.1          | Generating Modules for Macro-Cells   | 48              |

|   |                   | 3.1.1          | Generating Modules for FPGAs         | 48              |

|   |                   | 3.1.2<br>3.1.3 | Module Templates                     | 49              |

|   | 3.2               |                | bomy of an SDI Module                | 49              |

|   | 0.4               |                | Classes of Regularity                | 49<br>50        |

|   |                   | 3.2.1<br>3.2.2 | Geometric Hierarchy                  | 50              |

|   |                   | 3.2.2          | Structural Modules                   | 50<br>52        |

|   | 3.3               |                | le Generation in SDI                 | 52<br>53        |

|   | 0.0               | 3.3.1          | Paramog Architecture                 | 53              |

|   |                   | 3.3.2          | Design Cycle                         | 53              |

|   |                   | 0.0.4          |                                      | 00              |

|   |      | 3.3.3   | Module Parameters                       | 54 |

|---|------|---------|-----------------------------------------|----|

|   |      | 3.3.4   | Design Alternatives                     | 54 |

|   |      | 3.3.5   | Generator Output                        | 57 |

|   |      | 3.3.6   | XC4000-specific Features                | 58 |

|   |      | 3.3.7   | Implementation Details                  | 59 |

|   |      |         |                                         |    |

| 4 |      |         | lection and Floorplanning               | 63 |

|   | 4.1  |         | ization by Genetic Algorithms           | 63 |

|   | 4.2  |         | m Description                           | 63 |

|   | 4.3  |         | on Representation                       | 64 |

|   | 4.4  |         | ic Crossover Operators                  | 64 |

|   |      | 4.4.1   | Uniform Crossover                       | 65 |

|   |      | 4.4.2   | One-Point Crossover                     | 65 |

|   |      | 4.4.3   | Two-Point Crossover                     | 66 |

|   | 4.5  |         | ic Mutation Operators                   | 66 |

|   |      | 4.5.1   | Allel Mutation                          | 67 |

|   |      | 4.5.2   | Position Mutation                       | 67 |

|   |      | 4.5.3   | Translocation Mutation                  | 67 |

|   |      | 4.5.4   | Reversal Mutation                       | 68 |

|   | 4.6  |         | ic Inversion Operator                   | 68 |

|   | 4.7  | Multi-  | Criteria Evaluation                     | 68 |

|   |      | 4.7.1   | Net Delays                              | 69 |

|   |      | 4.7.2   | Compactibility                          | 69 |

|   |      | 4.7.3   | Fit into Target FPGA                    | 70 |

|   |      | 4.7.4   | Routability                             | 70 |

|   | 4.8  | Selecti | ion                                     | 70 |

|   |      | 4.8.1   | Elite Selection                         | 71 |

|   |      | 4.8.2   | Expected Value Selection                | 71 |

|   |      | 4.8.3   | Fitness Selection                       | 72 |

|   |      | 4.8.4   | Random Selection                        | 72 |

|   | 4.9  | Param   | neters and Dynamic Fuzzy-Control        | 72 |

|   |      |         | ilities and Limitations                 | 73 |

|   |      | -       |                                         |    |

| 5 | Fund |         | tals for Compaction and Microplacement  | 75 |

|   | 5.1  | Basics  | •                                       | 75 |

|   | 5.2  | Struct  | ure and Behavior of Digital Circuits    | 76 |

|   |      | 5.2.1   | Hierarchy                               | 76 |

|   |      | 5.2.2   | Regularity                              | 78 |

|   |      | 5.2.3   | Grouping Bits                           | 79 |

|   |      | 5.2.4   | Structure of Circuits: Network Skeleton | 80 |

|   |      | 5.2.5   | Behavior of Circuits: Network           | 83 |

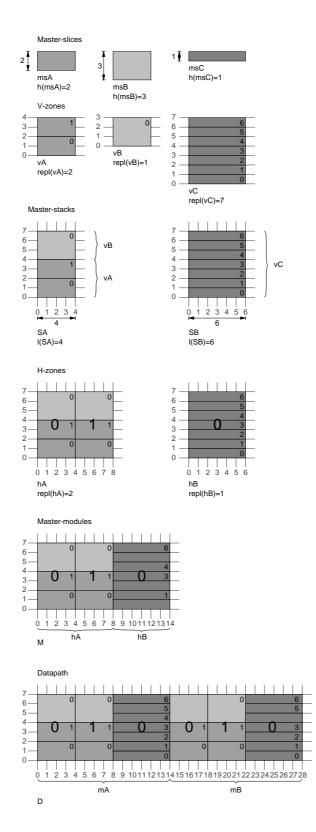

|   |      | 5.2.6   | Master-Slices and Slices                | 85 |

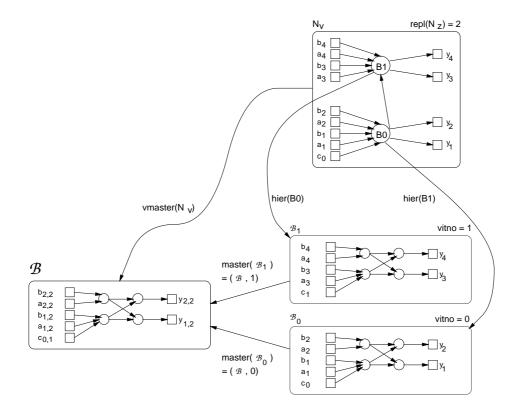

|   |      | 5.2.7   | V-Zones: Multi-Iteration Circuits       | 89 |

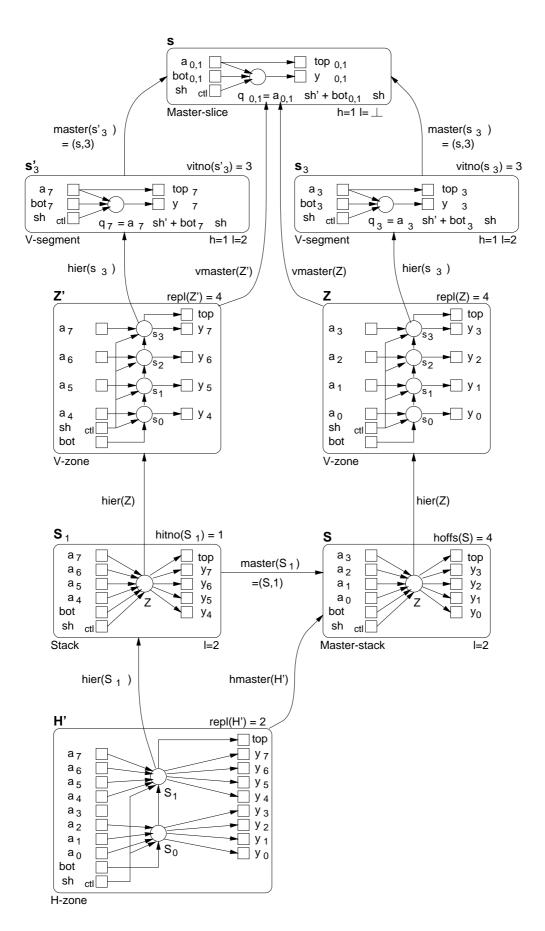

|   |      | 5.2.8   | Stacks: Multi-v-zone Structures         | 91 |

|   |      | 5.2.9   | H-Zones: Multi-Stack Structures         | 93 |

|   |      | 5.2.10  | Modules: Multi-h-zone Structures        | 95 |

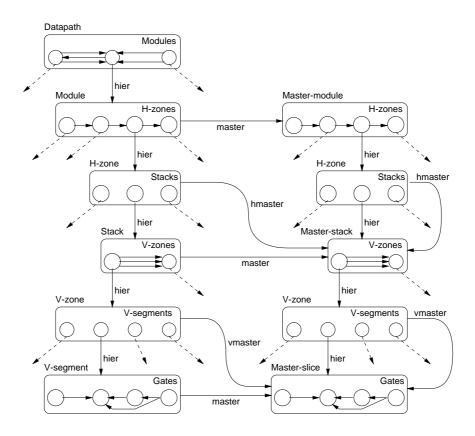

|   |     | 5.2.11  | Datapaths: Multi-Module Structures             | . 96  |

|---|-----|---------|------------------------------------------------|-------|

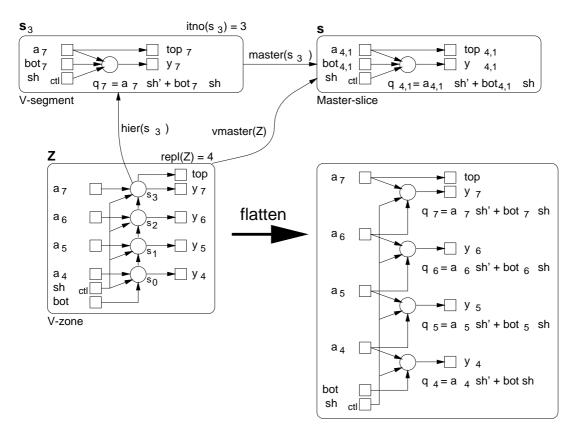

|   |     |         | P Flattening the Hierarchy                     |       |

|   | 5.3 | Topol   | ogical and Geometrical Layout                  | . 100 |

|   |     | 5.3.1   | Representing Geometrical Layout                |       |

|   |     | 5.3.2   | Representing Topological Layout                | . 101 |

|   |     | 5.3.3   | Describing Regular Bit-Sliced Layouts          |       |

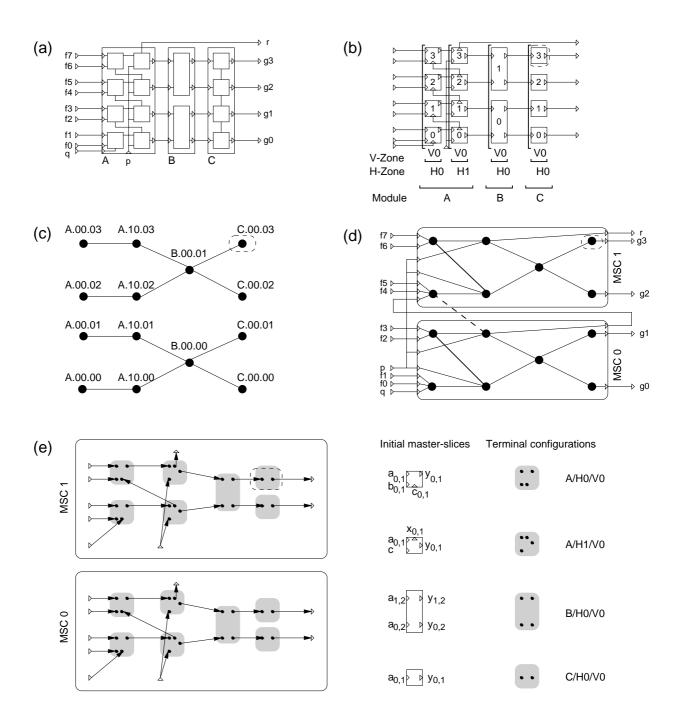

| 6 | Pea | ular Ca | ompaction                                      | 105   |

| Ŭ | 6.1 |         | ng Optimizable Areas                           |       |

|   | 6.2 |         | ening the Subdatapath                          |       |

|   | 6.3 |         | ture Extraction                                |       |

|   |     | 6.3.1   |                                                |       |

|   | 6.4 | Regul   | arity Analysis                                 |       |

|   |     | 6.4.1   | Building Terminal Graphs                       |       |

|   |     | 6.4.2   | Constrained Isomorphism                        |       |

|   | 6.5 |         | Optimization and Mapping                       |       |

|   |     | 6.5.1   |                                                |       |

|   |     | 6.5.2   | Pre- and Post-Compaction Isomorphism           |       |

|   | 6.6 | Sumn    | nary and Relations between Structures          |       |

|   | 6.7 |         | s on Placement                                 |       |

| 7 | Mic | roplac  | ement                                          | 125   |

| • | 7.1 | -       | cal Topological Placement                      |       |

|   | 7.2 |         | or Horizontal Geometrical Node Placement       |       |

|   | ••• | 7.2.1   | Determining the Placement Area                 |       |

|   |     | 7.2.2   | Node Placement                                 |       |

|   |     | 7.2.3   | Control Signal Routing                         |       |

|   |     | 7.2.4   | Critical Path Segment Delay Computation        |       |

|   |     | 7.2.5   | Maximal Critical Path Delay                    |       |

|   |     | 7.2.6   | Vertical Inter-omS Alignment                   |       |

|   |     | 7.2.7   | Objective Function                             |       |

|   | 7.3 | Efficie | ently Solving 0-1 ILPs                         | . 139 |

|   |     | 7.3.1   | Preprocessing and Constructive Enumeration     |       |

|   |     | 7.3.2   | Pruned Branch-and-Bound                        |       |

|   |     | 7.3.3   | Capabilities and Limitations                   |       |

|   | 7.4 | Heuri   | stic for Horizontal Geometrical Node Placement |       |

|   |     | 7.4.1   | Ensemble-Based Annealing                       | . 140 |

|   |     | 7.4.2   | Optimization Cost Function                     |       |

|   |     | 7.4.3   | Capabilities and Limitations                   |       |

|   | 7.5 | ILP fo  | or Vertical Geometrical Node Placement         | . 141 |

|   |     | 7.5.1   | Node Placement                                 |       |

|   |     | 7.5.2   | Vertical Distance in CLBs                      | . 142 |

|   |     | 7.5.3   | Recognizing Linear Horizontal Placement        | . 143 |

|   |     | 7.5.4   | Recognizing Horizontally Abutting Cells        |       |

|   |     | 7.5.5   | Recognizing Vertically Abutting Cells          | . 144 |

|   |     | 7.5.6   | Vertical SM Distance in a Single Column        |       |

|     |       | 7.5.7 Arc-Based Unit-to-Cell Assignment            | 146 |  |  |

|-----|-------|----------------------------------------------------|-----|--|--|

|     |       | 7.5.8 SM Distance in Adjacent Columns              | 147 |  |  |

|     |       | 7.5.9 Computing Net Delay in SMs                   | 148 |  |  |

|     |       | 7.5.10 Computing Path Delay in SMs                 | 149 |  |  |

|     |       | 7.5.11 Computing Maximal Critical Path Delay       | 149 |  |  |

|     |       | 7.5.12 Objective Function                          | 150 |  |  |

|     |       | 7.5.13 Solving the Vertical Microplacement 0-1 ILP | 150 |  |  |

|     | 7.6   | Handling Sequential Elements                       | 150 |  |  |

|     |       | 7.6.1 Placing Bound Flip-Flops                     | 151 |  |  |

|     |       | 7.6.2 Placing Floating Flip-Flops                  | 152 |  |  |

|     | 7.7   | Design Integration                                 | 153 |  |  |

| 8   | Exp   | erimental Results                                  | 155 |  |  |

|     | 8.1   | Tools Used                                         | 156 |  |  |

|     | 8.2   | Generic 16-bit Datapath                            | 157 |  |  |

|     |       | 8.2.1 Circuit                                      | 157 |  |  |

|     |       | 8.2.2 Processing                                   | 157 |  |  |

|     |       | 8.2.3 Performance                                  | 158 |  |  |

|     |       | 8.2.4 Comments                                     | 160 |  |  |

|     | 8.3   | 74181-based 32-bit ALU                             | 160 |  |  |

|     |       | 8.3.1 Circuit                                      | 160 |  |  |

|     |       | 8.3.2 Processing                                   | 160 |  |  |

|     |       | 8.3.3 Performance                                  | 160 |  |  |

|     |       | 8.3.4 Comments                                     | 163 |  |  |

|     | 8.4   | Address Generator for DES Encryption               | 163 |  |  |

|     |       | 8.4.1 Circuit                                      | 163 |  |  |

|     |       | 8.4.2 Processing                                   | 165 |  |  |

|     |       | 8.4.3 Performance                                  | 166 |  |  |

|     |       | 8.4.4 Comments                                     | 166 |  |  |

|     | 8.5   | Logic Unit of RISC CPU                             | 166 |  |  |

|     |       | 8.5.1 Circuit                                      | 166 |  |  |

|     |       | 8.5.2 Processing                                   | 166 |  |  |

|     |       | 8.5.3 Performance                                  | 169 |  |  |

|     |       | 8.5.4 Comments                                     | 169 |  |  |

|     | 8.6   | Discussion                                         | 169 |  |  |

| 9   | Sum   | mary and Future Work                               | 173 |  |  |

| Bil | oliog | raphy                                              | 176 |  |  |

| AŁ  | obrev | iations                                            | 188 |  |  |

|     |       |                                                    | 190 |  |  |

| 111 | dex   | ex I90                                             |     |  |  |

# **List of Figures**

| 1.1  | Conceptual FPGA architecture                                       | 5  |

|------|--------------------------------------------------------------------|----|

| 1.2  | Logic block architectures                                          | 7  |

| 1.3  | Routing architectures                                              | 8  |

| 2.1  | SDI overview                                                       | 11 |

| 2.2  | Xilinx XC4002 FPGA                                                 | 13 |

| 2.3  | Xilinx XC4000 configurable logic block                             | 14 |

| 2.4  | XC4000 switch matrix                                               | 14 |

| 2.5  | XC4000 single and double length lines                              | 15 |

| 2.6  | Connecting to long lines                                           | 16 |

| 2.7  | Signal delays on different routing resources                       | 16 |

| 2.8  | Enlarged section of Figure 2.7                                     | 17 |

| 2.9  | Example datapath providing simple arithmetic functions             | 18 |

| 2.10 | Classic datapath structures                                        | 19 |

| 2.11 | Folding modules jutting out of the placement area                  | 20 |

| 2.12 | Extents of datapaths and modules                                   | 21 |

|      | Matched and mismatched bit-slice pitch                             | 22 |

|      | Examples for BPLB values                                           | 23 |

| 2.15 | On-chip topology                                                   | 24 |

|      | SDI topology as used on the Sparxil processor                      | 25 |

|      | Regular structure of a module                                      | 26 |

| 2.18 | Examples for module layouts                                        | 27 |

| 2.19 | Multiple BPLB values in a single datapath                          | 29 |

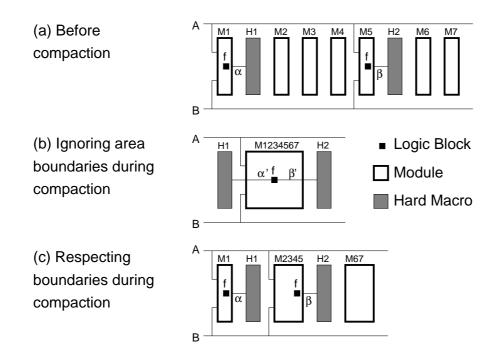

|      | Compaction                                                         | 30 |

| 2.21 | Wasted space in a module-based layout                              | 31 |

|      | Hard-macros as boundaries of compaction areas                      | 32 |

| 2.23 | Sample datapath segment                                            | 33 |

| 2.24 | H-zones and v-zones in a stack                                     | 35 |

| 2.25 | Floorplan context of an unplaced, compacted module                 | 36 |

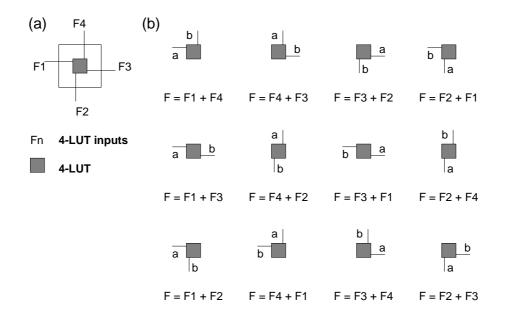

|      | LUT pin arrangement and configuration                              | 37 |

|      | Back-annotation of timing into optimized master-slice              | 38 |

| 2.28 | XC4000 CLB and corresponding regular cells                         | 39 |

|      | Interchangeable netlist cells in CLBs                              | 39 |

|      | Cell-based placement matrix                                        | 40 |

|      | Horizontal placement model                                         | 41 |

|      | Vertical placement model with example TTN routing lengths $d_{SM}$ | 43 |

|      | Real CLB routing structure (a) and abstract model (b)              | 44 |

| 2.34                                                                         | Design integration                                                                                                                                                                                                                                               | 45                                                               |

|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

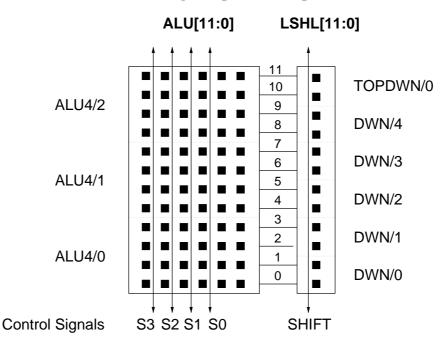

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9                  | Geometric regularities in a module                                                                                                                                                                                                                               | 51<br>52<br>54<br>55<br>56<br>57<br>58<br>59<br>61               |

| $\begin{array}{c} 4.1 \\ 4.2 \end{array}$                                    | Decaying population size during optimization                                                                                                                                                                                                                     | 73<br>73                                                         |

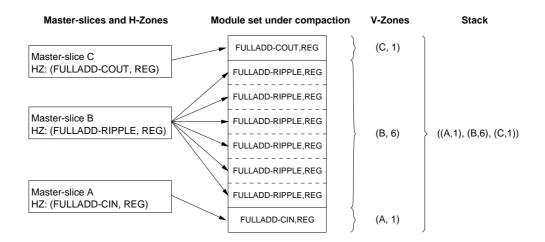

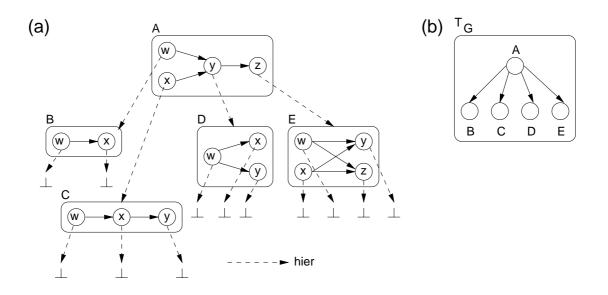

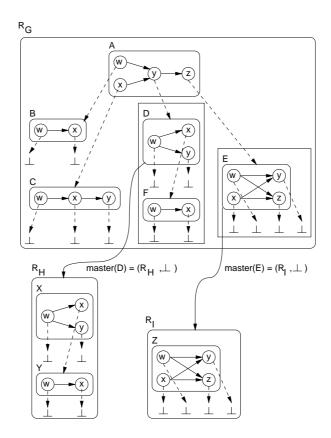

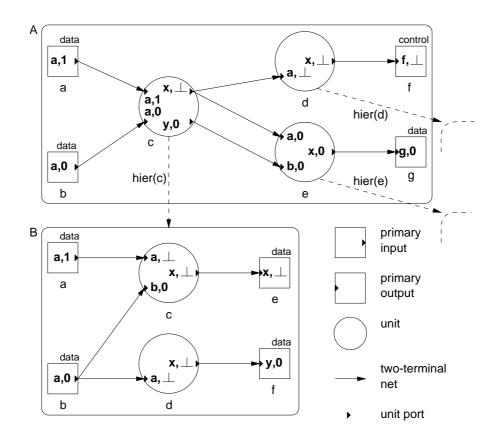

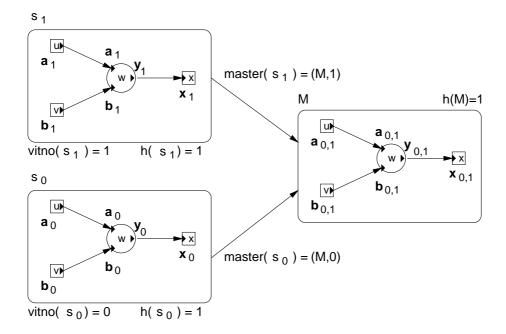

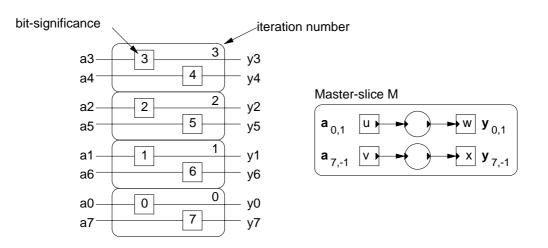

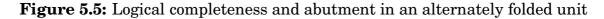

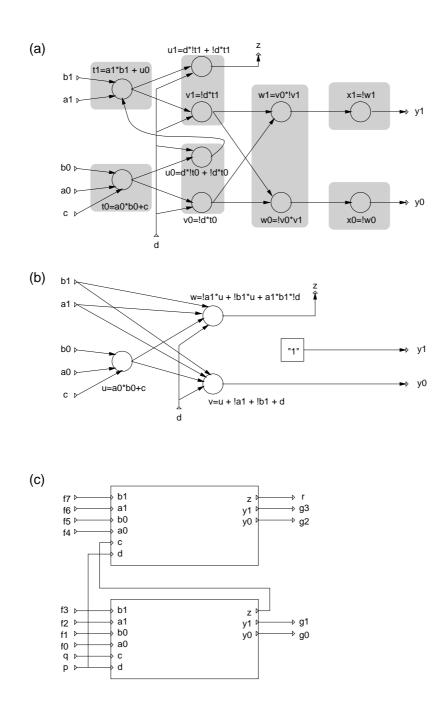

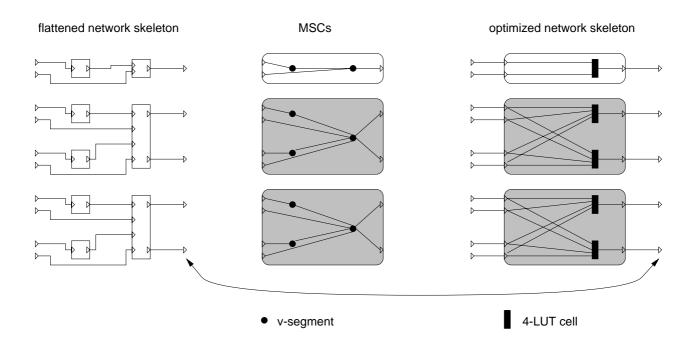

|                                                                              | (a) Graph hierarchy $T$ and (b) hierarchy tree $T_G$                                                                                                                                                                                                             | 77<br>79<br>83<br>86<br>88<br>90<br>94<br>97<br>98<br>100<br>104 |

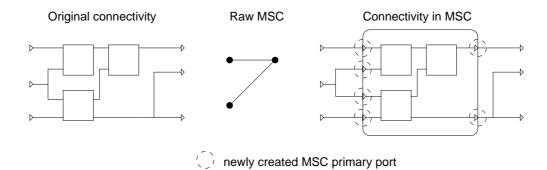

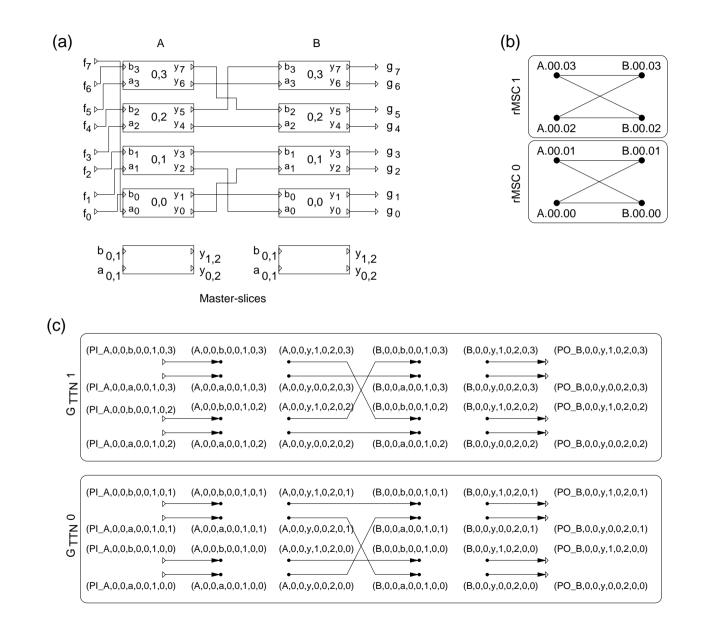

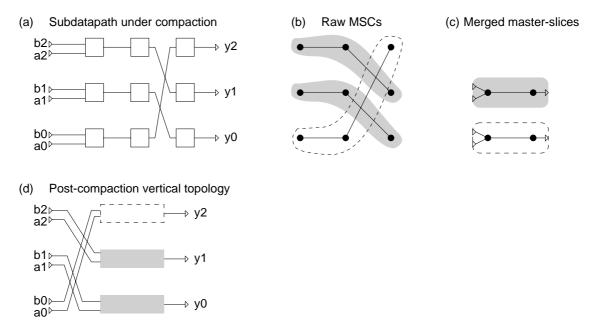

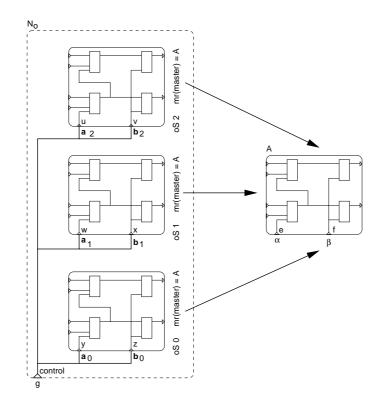

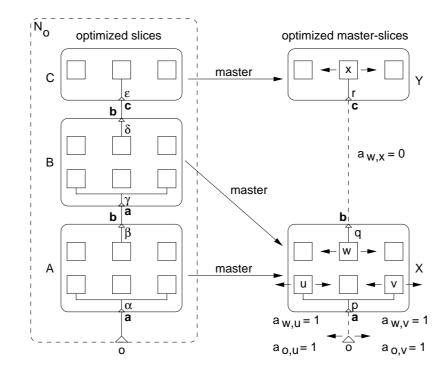

| $6.1 \\ 6.2 \\ 6.3 \\ 6.4 \\ 6.5 \\ 6.6$                                     | Applying Algorithm 3Flattening, structure extraction and regularity analysisCreating new primary ports in MSCsIncreased precision of terminal graphsEffects of logic processingIsomorphic correspondence between terminals on $N_f$ , $\mathfrak{M}$ , and $N_o$ | 108<br>109<br>112<br>113<br>121<br>122                           |

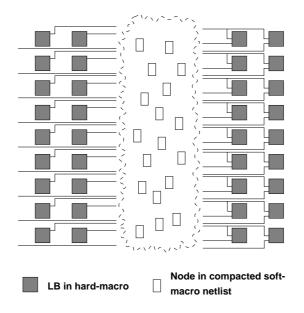

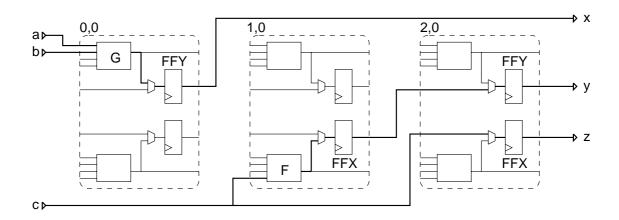

| $7.1 \\ 7.2 \\ 7.3 \\ 7.4 \\ 7.5 \\ 7.6$                                     | Post-compaction vertical topological re-placement.Control signal connectivity via VLL.Vertical inter-optimized master-slice alignment.Computing the set of nodes to align.Computing maximal critical path delay $dsm$ .Placing bound and floating flip-flops.    | 127<br>132<br>137<br>138<br>150<br>151                           |

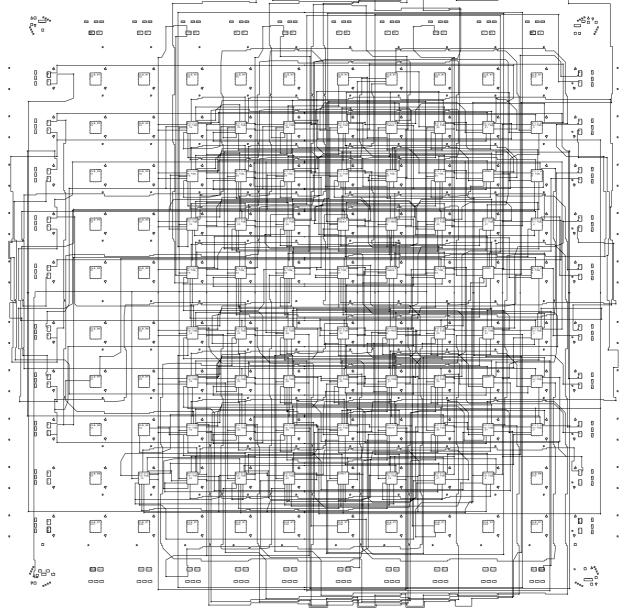

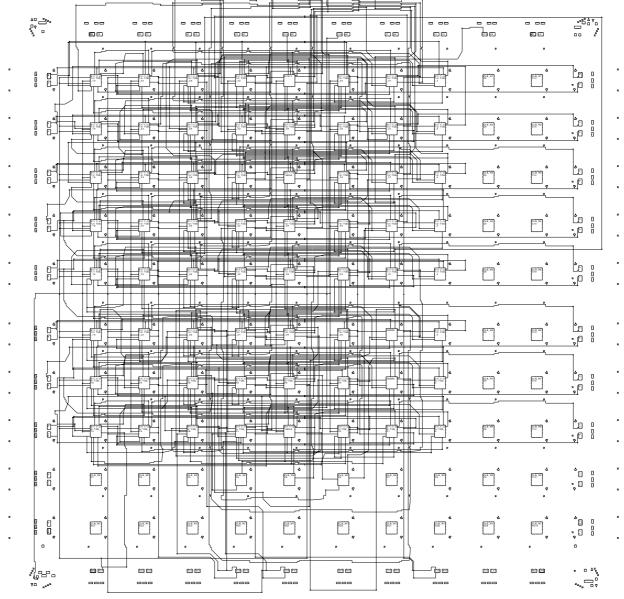

| $\begin{array}{c} 8.1 \\ 8.2 \\ 8.3 \\ 8.4 \\ 8.5 \\ 8.6 \\ 8.7 \end{array}$ | Single bit-slice of the example circuit                                                                                                                                                                                                                          | 157<br>158<br>159<br>161<br>162<br>164<br>165                    |

| 8.8  | UFC-A address generator implemented with XACT | 167 |

|------|-----------------------------------------------|-----|

| 8.9  | UFC-A address generator implemented with SDI  | 168 |

| 8.10 | SRISC logic unit implemented with XACT        | 170 |

| 8.11 | SRISC logic unit implemented with SDI         | 171 |

List of Figures

# List of Tables

| 2.1 | SDI module library overview                | 27  |

|-----|--------------------------------------------|-----|

| 3.1 | Current list of LPM modules                | 47  |

| 8.1 | Performance of generic 16-bit datapath     | 159 |

| 8.2 | Performance of 74181-based 32-bit ALU      | 161 |

| 8.3 | Logic processing statistics for 32-bit ALU | 163 |

| 8.4 | Performance of UFC-A address generator     | 166 |

| 8.5 | Performance of 32-bit SRISC logic unit     | 169 |

List of Tables

# List of Algorithms

| 1        | Deriving geometrical layout                                    | 102 |

|----------|----------------------------------------------------------------|-----|

| <b>2</b> | Find largest contiguous soft subdatapaths of datapath $D$      | 106 |

| 3        | Determine datapath $D_Q$ for the module sequence $Q \in C_D$ . | 107 |

| 4        | Finding raw master-slice candidates                            | 110 |

| <b>5</b> | Refining an rMSC into an MSC                                   | 111 |

| 6        | Create a terminal label                                        | 115 |

| <b>7</b> | Building terminal graphs                                       | 116 |

| 8        | Isomorphism constraints on terminal labels                     | 117 |

| 9        | Isomorphism constraints on terminal labels in TTNs             | 118 |

| 10       | Label-based test for constrained isomorphism                   | 118 |

| 11       | Regularity analysis                                            | 119 |

| 12       | Restoring vertical topological placement after compaction      | 126 |

| 13       | Determining the placement area per omS                         | 128 |

| 14       | Generating constraints for input control signal VLL routing    | 131 |

| 15       | Generating constraints for output control signal VLL routing . | 132 |

| 16       | Generating constraints for all segments on critical paths      | 135 |

| 17       | Generating constraints for vertical TTN delay in SMs           | 148 |

| 18       | Generating constraints for path delay in SMs                   | 149 |

| 19       | Computing switch matrix distances between arbitrary nodes      | 152 |

|          |                                                                |     |

#### LIST OF ALGORITHMS

## 1 Introduction

In the dynamic world of modern electronics, the counterpart to the mythical quest for the holy grail is the quest for a vorpal sword to fight the all-tooreal wyrm of increasing design complexity. Unfortunately, such a wondrous weapon has not been discovered yet, and the noble quest has turned more into the search for a better mousetrap. While the abovementioned wyrm will remain undaunted by the later, the lifes of countless engineers and circuit designers in the trenches will be eased by each gradual refinement to such basic an implement.

This work will describe one such improvement: A set of CAD tools, and a strategy for their use, to efficiently realize regular datapaths on field-programmable gate arrays. Despite being far from the wished-for dragonslayer (and more in the mousetrap league), the effects of this highly specialized method are quite appreciable when considered in a wider context.

With increasing chip complexities, the requirement for ever-higher performance, and steadily narrowing time-to-market windows, traditional design techniques are becoming more and more difficult to apply successfully.

Traditional quality control methods, such as simulation-based validation, become increasingly cumbersome to use. Especially when the complexity of the individual chip, which even today already encompasses dozens of millions transistors, is eclipsed by the larger complexity of multi-chip systems. E.g., current telecommunications systems require simulation patterns on the order of  $10^{11}$  of vectors [Qds96a] to support high confidence in the design. This huge number of vectors, combined with the changing requirement of running fewer, but longer simulations (to handle the growing complexity of implemented algorithms), instead of many shorter simulations, can no longer be processed in reasonable timespans. Even if an effort this massive is undertaken for a single chip, it usually cannot take system-level effects into account: Subtle interactions between multiple chips, especially with regard to rarely occurring boundary conditions, can usually only be discovered when observing an actually running system, instead of using human-devised test patterns [Qds96b]. The traditional breadboard-based prototyping using discrete components is often prohibited by the circuit or system complexity, or minimal real-time response requirements, however. Thus, another approach to the validation problem has to be found.

The quickly moving market also demands a hitherto unprecedented flexibility. Often, systems must be extremely adaptable to follow changing requirements such as upgrades of telecommunications standards, or new peripheral devices. While general purpose CPUs or DSPs could provide the maximum flexibility (all functionality implemented in malleable software), very fast processors are needed to meet the high performance requirements. Unfortunately, the considerable chip and system costs for these processors often precludes their use for all but very high-end applications.

For various applications, even the fastest available general purpose processors cannot provide the desired performance. Examples include particle detection and analysis in high-energy physics [NZKK94], or DNA sequence matching [BuAK96]. While an *application-specific integrated circuit* (ASIC) could fulfill the performance requirements, future changes can often only be anticipated by including a multitude of user-programmable parameters and operating modes on the chip. In addition to increasing the complexity of the basic design even more, this approach relies on the foresight and expertise of the designers to extrapolate all future usage variations. In case of an unforeseen variation, the ASIC becomes useless, or can only be used with considerable effort, performance degradation, or an expensive redesign.

In quite a few cases, *programmable logic*, especially in the form of fieldprogrammable gate arrays, can be a solution to the problems sketched above. The efficient application of FPGAs, especially their support by novel optimized CAD algorithms, will be at the center of this work.

The details of the programming process for FPGAs depend on the specific on-chip technology used. Common methods of configuration storage include E-PROM, EEPROM, SRAM and anti-fuses<sup>1</sup>. Anti-fuse, EPROM and EEPROM configurations are non-volatile, SRAM configurations are volatile in that the configuration must be battery-preserved, or be loaded from an external nonvolatile medium (ROM, external CPU etc.).

Especially re-programmable FPGAs can be used to perform validation by *emulation* instead of simulation [BEKS95]. Here, a single chip (or even an entire system) is partitioned into a number of FPGAs integrated with the remaining hardware components (e.g., peripheral devices, CPUs). In this manner, the complete system and environment are actually assembled in hardware, and can be used to perform conclusive system-wide tests (e.g., boot an operating system [Qds96b]), or be observed for billions of test vectors [Qds96a]. While the emulation speed is usually far slower than the target speed of the final ASIC (by a factor of 40 in [Qds96a]), it still exceeds simulation speeds by several magnitudes. Current emulation systems have capacities of millions of gates [Qds96c], and will benefit directly from the growth in FPGA capacities.

Non-reprogrammable FPGAs (e.g., anti-fuse-based) are unsuitable for fully automatic system emulation (no in-circuit reconfigurability). However, they can be used to extend the limits of traditional bread-board based prototyping approaches by integrating large amounts of formerly discrete logic into a single device.

The field-programmability of FPGAs also provides the required flexibility

<sup>&</sup>lt;sup>1</sup> An anti-fuse has a high-impedance state, but can be brought permanently into lowimpedance by briefly applying a (relatively high) programming voltage. In this manner, it can be used to selectively establish permanent connections.

in a world of short times-to-market and changing specifications. The critical path in a product cycle will be shorter due to the removal of long foundry lead times. Furthermore, the low NRE charges for FPGA-based implementations lower the cost of short-term design alterations (*engineering change order*, ECO), and thus significantly reduce the risk when tracking non-formalized standards. E.g., [3Com95] describes the design of a 10BASE-T Ethernet interface that was begun while the standards were still being formalized. By using FPGAs, the design could closely follow all changes in the emerging standard, and be released to the general market as soon as the standardization procedures were closed. Only after satisfying the initial demand with FPGA-based interfaces was a conversion to a classical gate array (to achieve lower unit costs) performed.

In-circuit programmable FPGAs are even more flexible: They allow hardware upgrades by simply shipping a new configuration bitstream (e.g., on a diskette or by network transfer [Xili96d]) to the customers. In this manner, hardware can be maintained as flexibly as software.

The basic performance of FPGAs is far slower than that of foundry-fabricated circuits. The delay of the fundamental elements (a gate for gate arrays, a logic block for FPGAs) differs by five orders of magnitude. However, reprogrammable devices can be configured with hardware specific to a given problem. E.g., for a certain dataset, the device might be loaded with a unit multiplying by a constant "5". Another dataset might lead to a multiplication by "42" being generated. By actually adapting hardware to low-level problem parameters, and employing specialties such as non-Von Neumann architectures, multi-stage pipelining, and problem-specific instruction sets, an FPGAbased configurable processor, also called *field-programmable custom computing machine* (FCCM), can outperform even the most powerful conventional computers on certain problems.

E.g., for DNA sequence matching, an FCCM based on an array of 248 processing elements<sup>2</sup> outperformed even MP-1 and CM-2 supercomputers by factors of 1344 and 7288 (respectively) [BuAK96]. A very simple FPGA-based co-processor [KoGo94], containing just three Xilinx XC4010 FPGAs and two 256K  $\times$  32 bit memory banks, can label objects in black-and-white images 6.5 times faster than a general purpose SPARC 20/71 workstation [Meye97] [Koch97b].

It is interesting to trace the development of programmable logic in a larger historical context. In contrast to traditionally fabricated chips, *programmable logic devices* (PLD) are sold as "blank" devices which can later be *personalized* with a specific design. Ideally, this process, also called *configuration* or *programming*, is performed without resorting to foundry techniques (etching, photolithography etc.). Depending on the nature of the device, configuration may be performed once or many times, using dedicated programming equipment, or by simple serial download to an already system-integrated device.

The various variants of programmable read-only memories (PROM, EPROM, EEPROM) may be viewed as PLDs: An  $2^n \times m$  PROM can be used to imple-

$<sup>^2\,</sup>$  Each based on a Xilinx XC4010 FPGA with 256K  $\times$  16 bits of local memory.

ment m combinational functions of n variables (using the memory to hold a truth table with  $2^n$  rows and m output columns). While the table-lookup character guarantees constant response times (without regard to the complexity of the function implemented), the memory size grows exponentially with the number of variables to evaluate, which becomes impractical for larger numbers of variables.

The next step in the evolution of PLDs was prompted by the insight that often only a small fraction of input variable combinations is relevant to the practical problem. Thus, it would suffice for the PLD to contain logic only for this subset of input combinations, and ignore the rest (*don't-cares*). This lead to the *programmable logic array* (PLA), a device implementing combinational functions in a sum-of-products form. A PLA consists of a configurable AND-matrix connected to an also configurable OR-matrix. By appropriately programming the AND-matrix, the product terms may be composed. The program for the OR-matrix then assembles sums from the selected product terms. Since the AND-matrix is programmable (instead of the fully decoded address evaluation in a memory circuit), only the relevant input combinations are evaluated.

To reduce the fabrication complexity of blank PLAs, and increase performance by reducing delay, a variant called *programmable array logic* (PAL) does away with the programmable OR-matrix. Here, each sum is composed from a fixed number of products.

The current generation of programmable arrays are devices called *generic array logic* (GAL), based on PALs. They also include sequential elements (flip-flops and latches), and internal connections to feed outputs back into the array. In this manner, they can directly implement state machines.

While the simple two-level structure of programmable arrays, also called *simple* PLDs (SPLD) leads to short circuit delays (around 5ns for fast commercially available chips), it also limits the design complexity: With an increasing number of product terms, the internal connection network (separate from the AND/OR logic functions) grows impractically large. Thus, current SPLDs usually have an upper limit around 200 equivalent gates [BrRo96].

Classical *mask-programmable gate arrays* (MPGA) allow the efficient implementation (60ps gate delay) of circuits with up to 12 million gates [Texa97]. Their "blank" chips, also called gate array masters, consist of a matrix of prefabricated transistors. An MPGA is personalized by applying final metal layers to interconnect the transistors in the desired manner. Unfortunately, this process relies on foundry equipment, and cannot be performed "in the field". Typical turnarounds are measured in weeks and months, and non-recurring engineering (NRE) charges begin at 10,000s of dollars.

Recently, *laser programmable gate arrays* (LPGA) have become available. Their blank chips include all metal connections between transistors. A laser beam is then used to remove all extraneous connections, leaving only those specified by the netlist. While personalization of LPGAs does not rely on foundry technology, the need for a precision laser cutter also makes it impractical for "in the field" prototyping. Still, with turnarounds reduced to a few days, and NRE charges starting at under \$10,000, LPGAs are very attractive for low-volume designs of up to 70k gates, with a gate delay of 300ps [Chip97].

The main advantage of MPGAs over SPLDs is the scalability of their structure: In contrast to SPLDs, logic functions and interconnect are not implemented independently of each other, but rely on the same resources (transistor matrix). Thus, when increasing the area for logic functions, the area for interconnect also increases (and vice versa).

The *field-programmable gate array* (FPGA), invented in 1985 by Xilinx Inc., combines the easy "in the field" programmability of SPLDs with the scalable logic and interconnection structure of MPGAs, allowing a currently available maximal capacity of 85k gates [Xili97], and near-term projected capacities of up to 400k gates [Acte96].

Unfortunately, the development of FPGA-specific CAD tools has not kept up with the growth in chip capacity. Many of the current tools trace their ancestry to a time, when FPGAs could only hold a thousand gates, and were primarily used to implement glue logic. When attempting to implement the more complex datapath structures common to many of today's CPUs and DSPs in one of these larger FPGAs, the traditional tools are often overtaxed. The resulting circuits are often inefficient in terms of area use and performance. This work will describe a suite of CAD tools, and a strategy coordinating their use, specialized for efficiently mapping datapaths onto FPGAs.

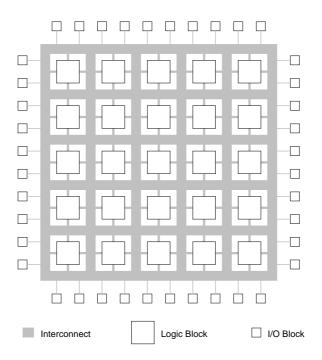

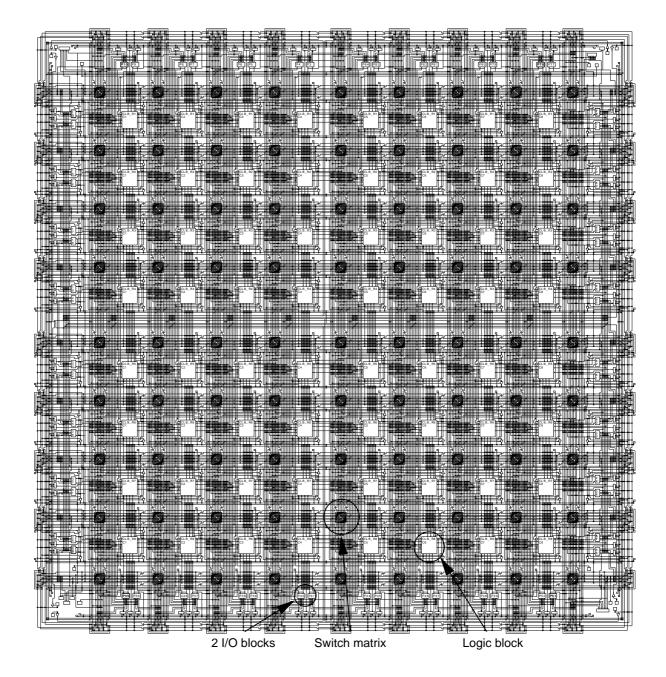

Figure 1.1: Conceptual FPGA architecture

Figure 1.1 shows the fundamental elements of a conceptual FPGA [BFRV92]. It consists of a number of programmable *logic blocks*, interconnected by a programmable *interconnection network*. Programmable *input/output blocks* at

#### 1 Introduction

the periphery of the chip allow for chip-external communication.

The implementation of a circuit on an FPGA consists of three main steps:

- 1. The circuit netlist is *partitioned* into individual logic blocks (each of which can hold only a relatively small part of the logic). The result is a netlist of logic block configurations.

- 2. Each logic block configuration is then assigned to an actual logic block on the FPGA (*placement*).

- 3. The interconnection network is programmed for the connectivity proscribed by the netlist (*routing*).

All of these steps are highly dependent on the actual structures (*architec-ture*) of logic blocks and routing network. See [BFRV92] for a detailed discussion including a statistical analysis of different architectures. The next few paragraphs will present brief overviews of general logic block and routing architectures. An actual FPGA, the Xilinx XC4000 series, will be examined in greater detail in Section 2.1.

It is the fixed FPGA architecture that distinguishes CAD tools for FPGAs significantly from those for classical standard cell or gate array technologies. In an FPGA, it will not be possible, e.g., to simply increase the width of a routing channel to handle congestion: The channel width has been fixed on the FPGA die at fabrication time, and cannot be influenced by the user. Due to the long interconnection and logic block delays, even slightly suboptimal partitioning, placement, or routing can cause a significant performance degradation. Efficient CAD tools will have to be finely tuned to exploit a given FPGA target architecture for optimal results. To this end, our back-end tools have detailed knowledge about the capabilities of logic blocks, and the intricacies of the interconnection networks. In addition, however, we follow a two-pronged approach by also specializing the front-end for the regular datapath structures we intend to implement. In this manner, we can cover precisely those areas neglected by the current general-purpose tools.

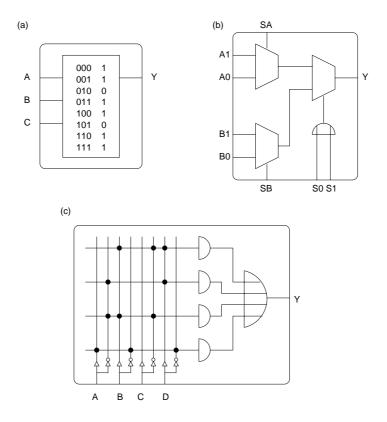

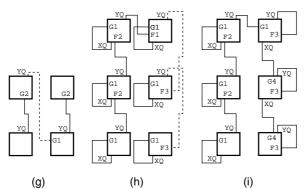

The nature and size of logic that fits into a single logic block is determined by the logic block architecture. A logic block can be as primitive as a simple transistor pair [Cros94], or be as complex as to contain an integer multiplier, two ALUs, six registers and three local memories [EbCF96]. The most common logic blocks are based on one or more k-input lookup-tables (k-LUTs) (Figure 1.2.a) [Alte95] [ATTM95] [Xili96a] [Xili96b] [Xili96c], multiplexers (Figure 1.2.b) [Acte95a], or on a PAL-like internal structure (Figure 1.2.c) [Alte96] [AMDI96]. Often, they also contain sequential elements such as flipflops or latches (not shown in Figure 1.2). Small logic blocks (in terms of logic capacity) are called *finely granular*, otherwise they are called *coarsely granular*.

Since the signal delays within a logic block are usually far shorter than those encountered when routing a signal through the general interconnection network, many current FPGAs are coarsely granular. However, for an efficient

Figure 1.2: Logic block architectures: (a) look-up table, (b) multiplexer, (c) PAL

mapping to these chips, the large capacity of the logic blocks actually has to be filled. Due to their larger size (in terms of silicon area), a coarsely granular FPGA will have fewer logic blocks than a finely granular FPGA of the same gate capacity. Thus, partially filled coarsely granular blocks will waste a much larger fraction of chip gate capacity than partially filled finely granular blocks. To minimize this wastage, our system contains dedicated optimization passes aiming to maximally fill each logic block.

The routing architecture influences the performance of the FPGA-implemented circuit as well as the speed of the implementation process. A fast routing network will allow short connections between logic blocks. A very general routing network (e.g., a fully populated crossbar) will only need minimal computational effort to determine a configuration which provides the desired connectivity. More constrained architectures (e.g., connectable metal segments with varying lengths) require more complex routing algorithms.

However, the capabilities (speed and flexibility) of the routing network are limited by the silicon area available for its implementation. Thus, the design of a routing architecture is constrained by conflicting requirements:

1. **Capability**: All required connections should be routable with minimum delay. However, more flexible routing networks may consume more silicon area.

#### 1 Introduction

2. **Silicon area**: Since the die size of a chip is limited, a more flexible routing network consumes area possibly better used by logic blocks. However, a small but overconstrained routing architecture might hamper circuit performance (by forcing long "detour" connections), or even prevent the circuit from being routed at all (insufficient routing resources).

Note especially the last point: The number and layout of routing resources (similar to "channels" in standard cell technologies) on an FPGA is fixed at "blank" chip fabrication time. Thus, circuits to be used on this FPGA type have to get by with the resources available, or cannot be implemented at all on the given FPGA type. The full-custom and standard cell routing techniques of just increasing the channel widths in congested areas are unavailable on FPGAs, making efficient FPGA routing considerably more difficult.

While interconnection delay on FPGAs is also dependent on wire lengths and capacities, it depends primarily on the number and nature of programmable connections (anti-fuses, pass transistors, transmission gates, multiplexers), called *switches*, that the signal passes from source to sink.

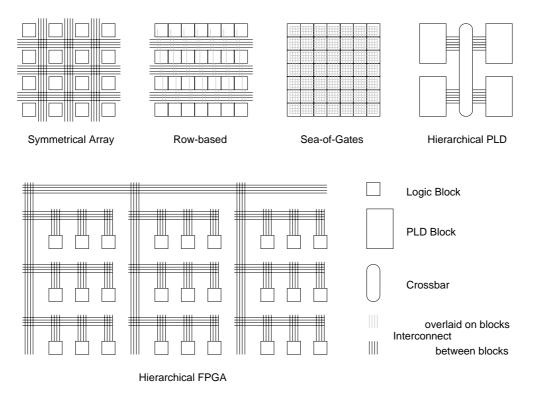

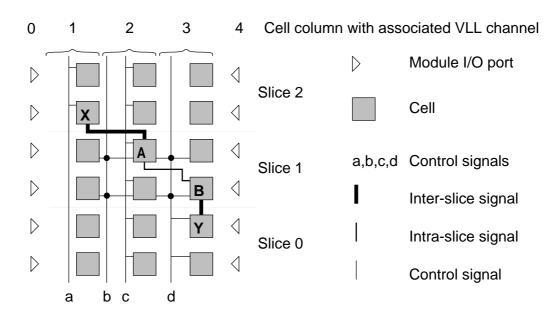

Figure 1.3: Routing architectures

The most common routing architectures used today are shown in Figure 1.3. Assume that switches are placed at all wire intersections (but see Section 2.1). Without going into a more detailed discussion, in symmetrical arrays, row-based FPGAs and sea-of-gates FPGAs, geometrically adjacent logic blocks will have short interconnection delays (few switches in the signal path). FPGAs composed as hierarchical PLDs usually have distance-independent

routing delays due to the (fully or partially populated) crossbar switch at the center of the chip. Routing delays on hierarchical FPGAs, however, are not proportional to geometrical distance. E.g., assume a source to be placed in the bottom-right logic block, and a sink in the logic block directly above it. While the logic blocks are adjacent, the signal has to cross three routing hierarchy levels (six switches) before it reaches its destination. Many FPGAs support a mix of routing architectures (e.g., a symmetrical array combined with hierarchical elements), or special features not covered by the general model. These might include dedicated resources for routing clock signals, or for distributing high fan-out signals with low skew over long distances.

As with logic block architectures, a good FPGA CAD tool needs to take the specific details of the target FPGA's interconnection network into account. Our system exploits these resources by mapping higher-level concepts (such as inter-bit-slice control signals) recognized by the front-end directly to their most efficient counterpart on the physical level.

By combining a front-end specialized for a specific class of circuits (wide regular datapaths, as needed in FCCMs and fast ASIC emulation) with a backend optimized for the target FPGA architecture, we are able to generate faster circuits in shorter amounts of computation time. Given the abovementioned wide applicability of FPGAs in a modern VLSI design, even gradual improvements to small parts of a such a circuit can have appreciable effects on the entire system.

It's been said: "Build a better mousetrap, and the world will beat a path to your door." But that's not the purpose of a mousetrap, is it? – Eric S. Raymond on USENET

### 1 Introduction

## 2 Overview of Structured Design Implementation

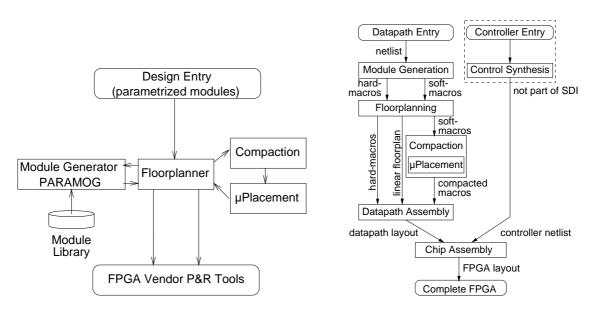

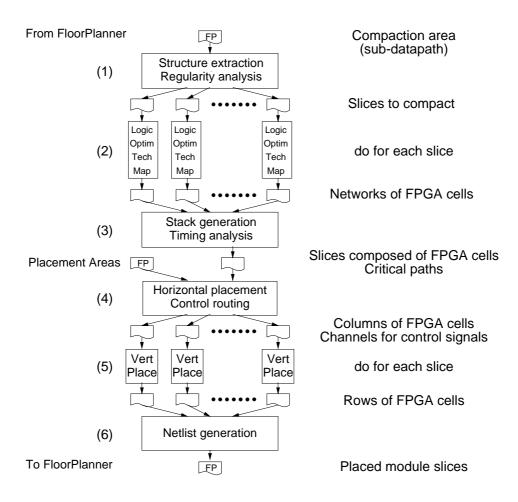

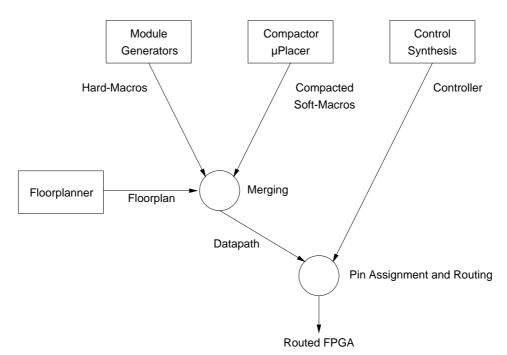

The points raised in Chapter 1 lead to *Structured Design Implementation* (SDI), a strategy for the efficient implementation of bit-sliced datapath structures on FPGAs. Bit-sliced architectures are called *regular* in context of SDI. The general organisation of the strategy and the design flow is shown in Figure 2.1 and outlined in the following sections.

This chapter presents an easily accessible overview of the entire system, while Chapters 3 to 7 will describe key components in greater detail or more formally.

SDI does not consist of a single tool, but a suite of specialized tools and a strategy coordinating their application. The suite combines a floorplanner, module generators, and tools for placement and global routing with minimization and technology mapping algorithms. It is thus difficult to compare it with specialized stand-alone tools that cover only part of the design implementation process, but these tools can often be integrated into SDI with minimal effort (see Section 2.6).

(a) System Architecture

(b) Design Flow

Figure 2.1: SDI overview

### 2.1 Xilinx XC4000 FPGAs

To better understand the design decisions made during the development of SDI, it is helpful to examine the architecture of the currently targeted FPGA in greater detail. The Xilinx XC4000 series, one of the most popular chips, is a third generation FPGA and was introduced by Xilinx Inc. in 1990. Later revisions, such as the XC4000A, XC4000E, XC4000EX, and XC4000XL series, improve upon various details (e.g., routing facilities, synchronous on-chip memories etc.), but much of the basic design is still unchanged. The XC4085XL FPGA has a capacity of 85k gates and is currently (June 1997) the highest density device available<sup>1</sup>. With logic block delays of 1.3ns in the "-1" speed grade, XC4000EX-1 and XC4000XL-1 chips are also among the fastest current chips.

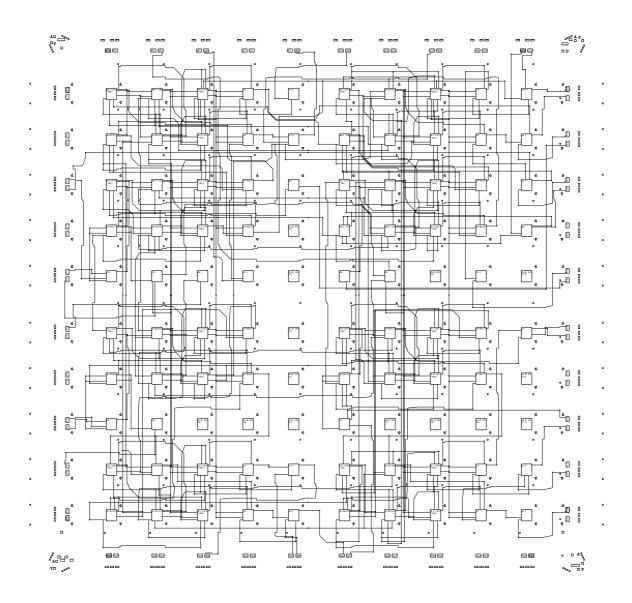

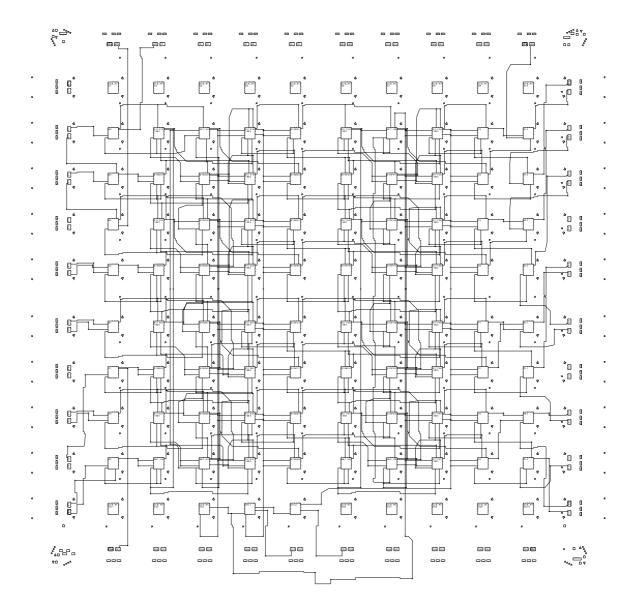

Figure 2.2 shows a "blank" XC4002 FPGA. The basic layout is very similar to the conceptual FPGA of Figure 1.1, with the routing architecture being a symmetrical array (Figure 1.3). The I/O blocks (IOB) are located at the sides of the array.

XC4000 FPGAs also have various special features not part of the conceptual FPGA. These include wide edge decoders, the use of logic blocks as fast on-chip 32x1 bit or 16x2 bit memories, a fast carry-propagation logic for adders and counters, and on-chip tri-state buffers (TBUF).

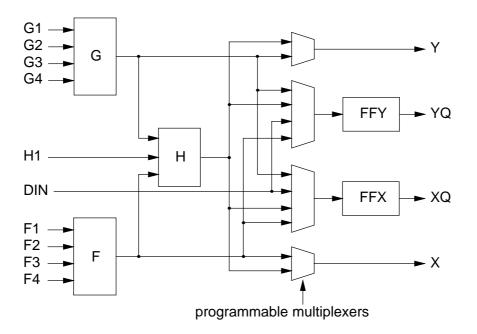

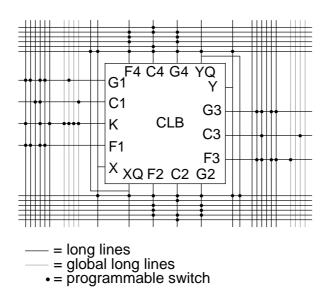

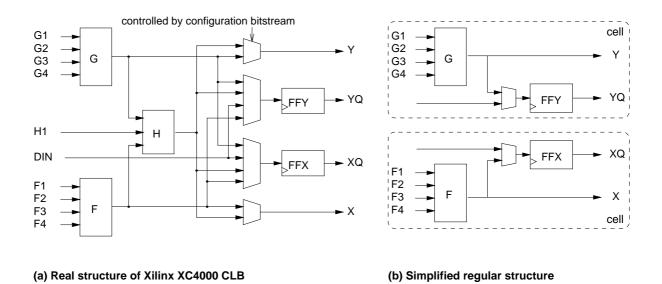

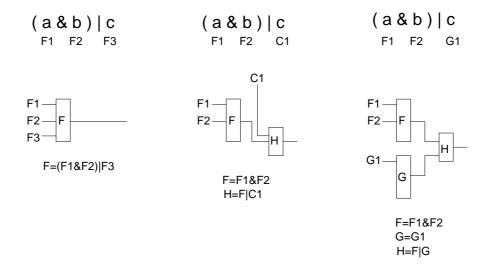

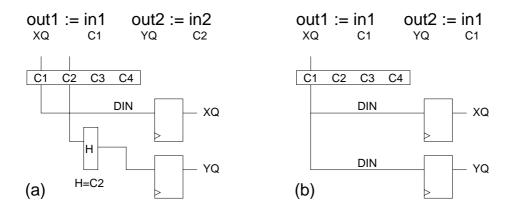

#### 2.1.1 Logic Block Architecture

The logic blocks on an XC4000 FPGA are called *configurable logic blocks* (CLB). A simplified view of the internal structure is shown in Figure 2.3. Basically, a CLB consists of two 4-LUTs F and G, and a 3-LUT H. Furthermore, it contains two D-flipflops FFX and FFX. Some connections are hardwired (e.g., the H LUT accepts inputs only from the outputs of the F and G LUTs, and the H1 CLB input pin. However, others can be established at configuration time using a network of programmable multiplexers. In this manner, e.g., the output of the H LUT might be routed to the Y CLB output pin, or the DIN CLB input pin connected to the input of the FFX D-flipflop.

A single CLB may implement any two independent functions of two variables, any one function of five variables, any function of four variables together with a single of *some* functions of five variables, or some functions of up to nine variables.

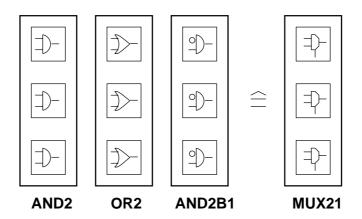

Due to the large logic capacity of a CLB (as compared to transistor pairs and multiplexers), XC4000 FPGAs have a coarse granularity. Consider, e.g., the amount of CLB capacity wasted when implementing only a simple twoinput AND gate in a single CLB. Thus, for the XC4000, the method of "packing" logic into CLBs with minimum wastage and delay becomes very important.

$<sup>^1</sup>$  Note that in order to obtain this much *configurable* capacity, the FPGA chip itself has 16 million transistors, three times the number in Intel's PentiumPro CPU [Xili97].

Figure 2.2: Xilinx XC4002 FPGA

Figure 2.3: Xilinx XC4000 configurable logic block

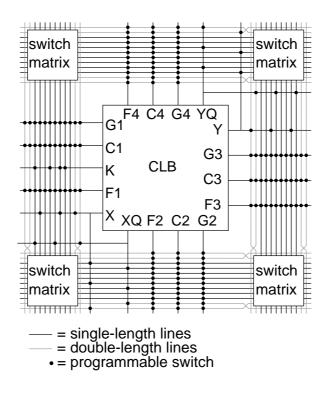

#### 2.1.2 Routing Architecture

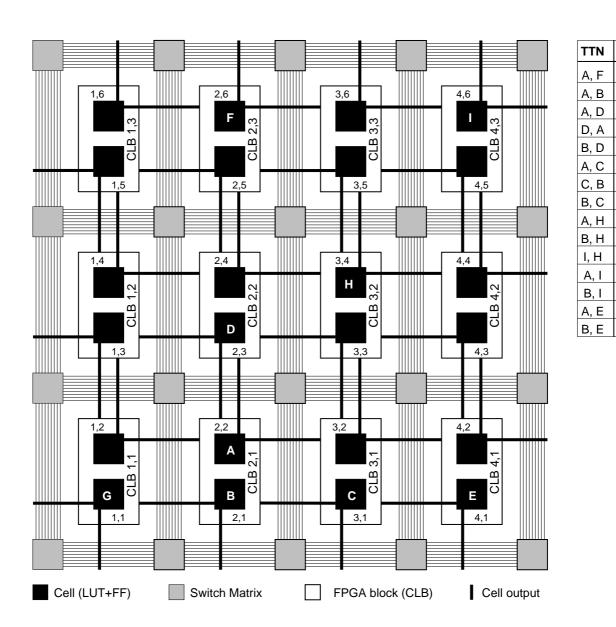

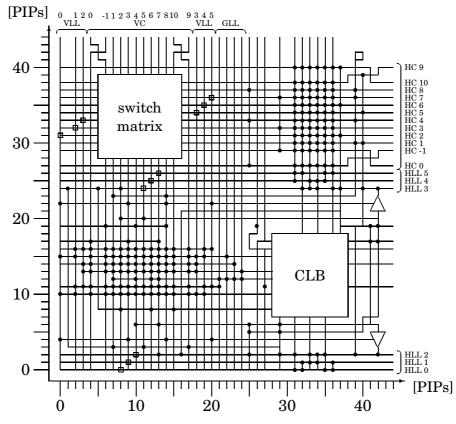

As shown in Figure 2.2, an XC4000 FPGA consists of a symmetrical array of logic blocks, with metal segments of varying lengths placed between the logic blocks. Programmable connections, called *switch matrices* (SM), at the intersections of horizontal and vertical metal segments, allow the interconnection of individual segments to cross longer routing distances, possibly also routing a signal around a corner.

Figure 2.4: XC4000 switch matrix

Figure 2.4 shows a switch matrix and two of the possible connections. Note that, to conserve silicon area, a SM is no fully populated crossbar, but provides a more constrained connectivity: A signal entering at pin  $n \in \mathbb{N}$  at side  $k \in \{N, S, E, W\}$  can only be routed to pin n at the sides  $\{N, S, E, W\} \setminus \{k\}$ .

While a routing architecture just based on SMs and wires of a single length (one logic block) could certainly work, its performance would be limited by the increasing number of slow switches between source and sink of a net: E.g., to connect a logic block in row 1, column 1, with a logic block at row 1, column 6,

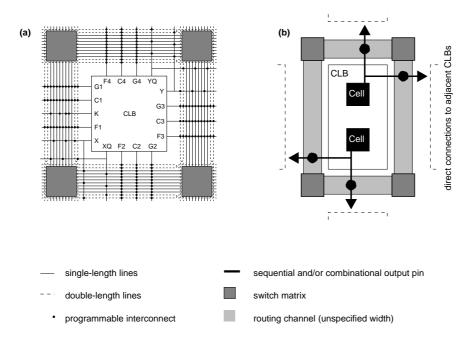

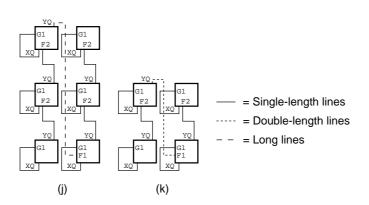

Figure 2.5: XC4000 single and double length lines

the signal would have to pass through five SMs, each with a resistance of 1-2  $k\Omega$ , and capacitance of 10-20 fF.

To counter this effect, XC4000 FPGAs use different length metal segments. Single length lines are only a single CLB long, while double length lines have a length of two CLBs. The result is shown in Figure 2.5. The CLB pins can be connected to the metal segments forming the routing network through individual programmable switches. The single length lines (shown in black) run between a pair of adjacent SMs. Double length lines (shown in grey), pass only through every second SM (see also Figure 2.5). While this limits their flexibility somewhat (e.g., the signal cannot turn around a corner at an arbitrary SM), it also decreases signal delay by halving the number of switches in the signal path.

For even longer distances, the XC4000 routing architecture provides *horizontal* and *vertical long lines* (HLL, VLL): Long metal segments running across half the height (VLL) and length (HLL) of the chip, unbroken by any switch matrix. For increased flexibility, two horizontal or vertical long lines may be interconnected (using programmable switches at the center of the chip) to route a signal along the entire length or height of the FPGA. Figure 2.6 shows how CLB pins can be connected to the long lines.

When a signal has to be routed to every CLB on the FPGA (e.g., clocks), *global long lines* may be used. While only four global long lines exist in the XC4000 series (also shown in Figure 2.6), they can supply a large number of sinks with very low skew.

Newer revisions such as the XC4000EX and XL extend this routing scheme

#### 2 Overview of Structured Design Implementation

Figure 2.6: Connecting to long lines

with additional resources such as direct interconnections for very fast connectivity between adjacent CLBs, and quad and octal length lines for fast medium-range connections (an extension of the double length line concept). Furthermore, they also increase the actual number of metal segments available.

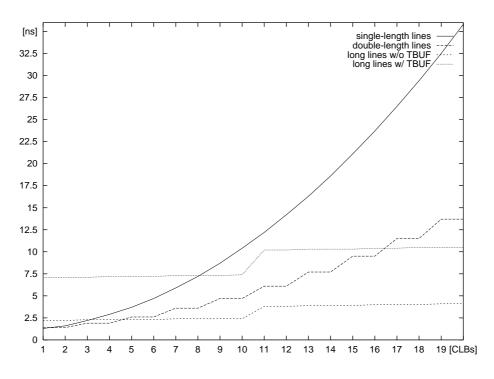

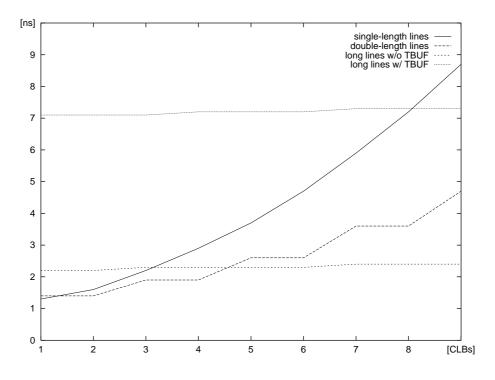

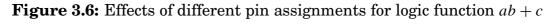

Figure 2.7: Signal delays on different routing resources

The three level routing (single, double, long lines) of the XC4000 leads to

Figure 2.8: Enlarged section of Figure 2.7

the delays graphed in Figures 2.7 and 2.8<sup>2</sup>. The X-axis shows the total net load (fanouts) and the distance to the farthest CLB, the Y-axis the delay in ns. Note the reduced slope of the double length line vs. the single length line delay. Furthermore, long line delay is almost completely independent of routing distance and net load, and increases only when the programmable switches at the chip center are crossed (between CLBs 10 and 11 on the XC4010-5). Some of the horizontal long lines have connections to TBUF outputs for implementing on-chip tri-state busses. The capacitive loading of these outputs slows these long lines down considerably.

Returning to Figure 2.5, note the placement of input and outputs around a CLB: While inputs can be routed into the CLB from any direction (the input pins of a LUT are interchangeable), the outputs have preferred directions. The X and XQ outputs most efficiently supply sinks located below and left of the CLB, while the Y and YQ outputs should be used for sinks above and right of the CLB.

# 2.2 Structured Design Entry

We concentrate on implementing regular datapaths using a regular on-chip layout, and will rely on traditional methods to handle irregular circuits such as controllers. Thus, we need to derive information describing the regular (bit-sliced) structure from a given circuit description. Since SDI handles only regular structures, our input format can afford to be specialized for this do-

$<sup>^2</sup>$  Delay times were experimentally determined on an XC4010-5.

main. So instead of extracting regularity information from a generic netlist (as in [OdHN87], [ChCh93], [YuWY93], [NaBK95]), or evaluating manually annotated regularity attributes (e.g., [ATTM94]), datapaths are entered into SDI in the form of interconnected parametrized modules that encapsulate the bit-sliced structure.

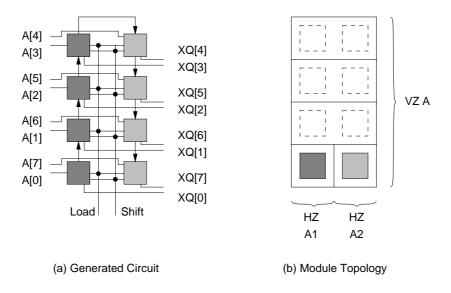

**Explanation 1** A *module* is a sub-circuit, described at varying degrees of abstraction (behavioral, structural, layout). *Parametrized* modules do not have a static description, but rely on a static *template* combined with dynamic property-value assignments, to create an adapted description at instantiation time. *Regular* modules have a description that follows a consistent pattern: A module consists of instances (copies with actual parameters) of masters (templates with formal parameters). A bit-sliced structure is a special case of a regular module that is also a regular array (Section 3.2.1).

To measure the regularity of a given structure, the *regularity index* of [Leng86] can be applied. It is defined as the ratio of actual components (instances) to the number of original templates (masters). The regularity index of common circuits is currently in the range 10...100.

In the context of this work, we will concentrate on the processing of automatically generated (Section 2.4) bit-sliced parametrized modules, just called modules for brevity. While SDI can also process non-bit-sliced modules, they will be treated as "black-boxes" and not optimized further (Explanation 5).

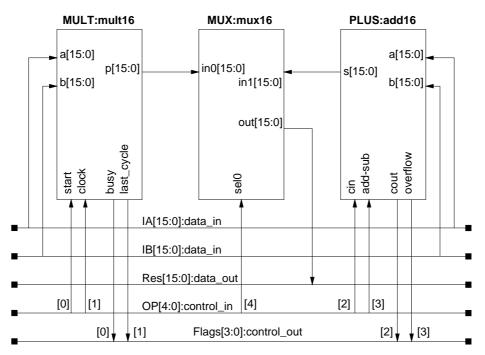

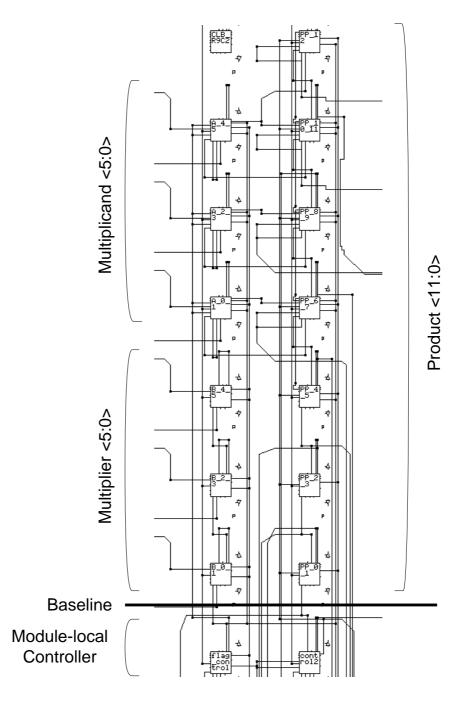

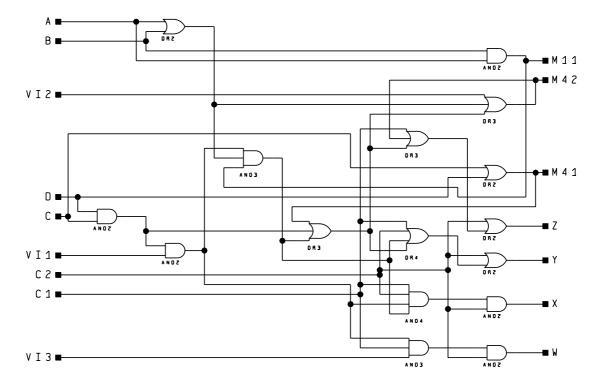

Figure 2.9: Example datapath providing simple arithmetic functions

Designs are expressed in the SDI netlist format *SNF*, which is a textual netlist of module declarations, module instantiations, and interconnections. It also associates values with module parameters such as bus widths, data

types, and optimization requests (speed vs. area). Furthermore, SNF allows to clearly differentiate between data and control signals. A typical example for a datapath expressible in SNF is the fragment shown in Figure 2.9. It calculates either the sum, the difference, or the product of two data operands IA and IB and puts the results on an data output bus Res. The specific operation performed and additional information (e.g., carry initialization) is entered through the control input bus OP. Status information monitoring the progress of the datapath (e.g., busy) or arithmetic flags are made available to the outside on the control output bus Flags. A detailed description of the format can be found in [Putz95a].

In this manner, information on the logical structure of the circuit is passed down from design entry to the placement and routing tools, and does not have to be reconstructed from an unstructured, possibly flattened netlist. The preserved regular structure can then be used to optimize the circuit as well as the internal operation of the electronic design automation (EDA) algorithms.

# 2.3 Target Topology

# 2.3.1 Datapath Topology

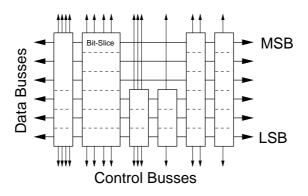

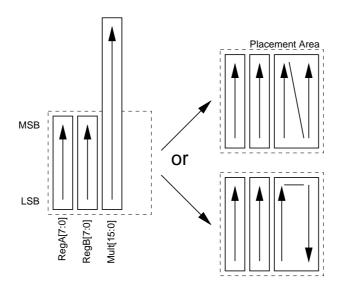

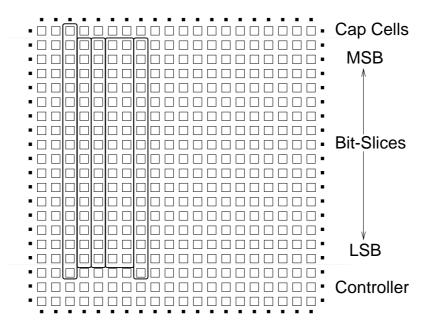

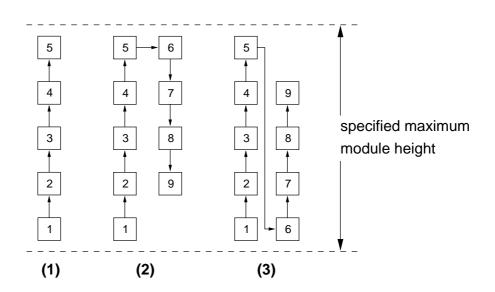

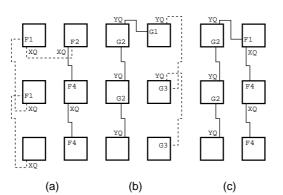

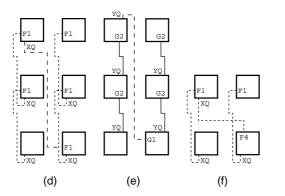

In holding with the classical approaches (e.g., [CNSD90], [BeGr93], [Raba85], [GrPe97], [Shro82]), SDI assumes that a datapath is laid out as a linear placement of modules, with each module consisting of stacks of bit-slices (Figure 2.10). Within the datapath, all modules usually have a consistent stacking direction for the bit-slices from least-significant bit (LSB) to most-significant bit (MSB). However, this direction may change locally to accomodate *folded* modules that are too tall for the placement area (Figure 2.11). In holding with the traditional approach, control and data flows are generally orthogonal to each other.

Figure 2.10: Classic datapath structures

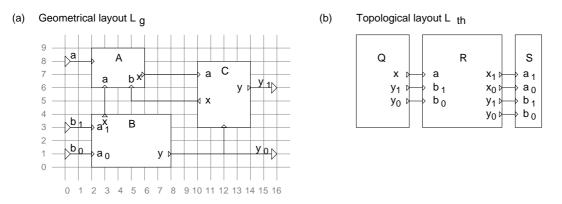

When describing the layout and topology of datapaths or modules, it is useful to differentiate between an unplaced datapath *logical circuit*, and its placed *physical layout*. Placement is differentiated into the *geometrical place*-

Figure 2.11: Folding modules jutting out of the placement area

*ment* of a layout at an explicitly specified location on the die, and the *topological placement* of a layout relative ("above", "left-of", etc.) to another.

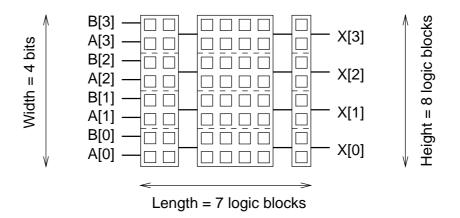

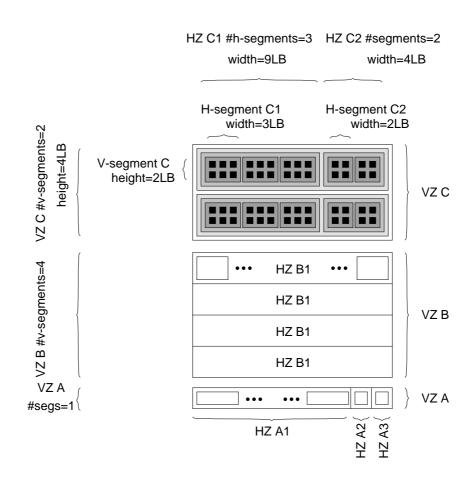

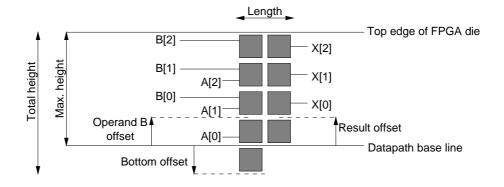

To this end, we introduce the quantities of *width*, *height*, and *length*. Figure 2.12 illustrates their relationship.

**Explanation 2** The logical *width* of a datapath or module circuit is the maximum number of differently significant bits processed in parallel. *Height* and *length* refer to the size of the bounding box of the physical datapath layout, with height being measured in the direction of width. Height and length are expressed in technology-dependent units, with logic blocks (LB) being most appropriate for FPGAs.

The restriction "differently significant" in the explanation of width serves to more clearly describe the logical structure of arithmetic units in the datapath. For example, while a 32-bit adder with operands A[31:0] and B[31:0] has 64 input bits, each two of these input bits will have the same significance in the input words (e.g., A[0] and B[0], A[1] and B[1], etc.). Since the data flows in the datapath should be correctly aligned (usually at the LSB, as in Figure 2.10), the physical datapath layout is directly influenced by this logical characteristic.

In full-custom and macro-cell technologies, cell placement and routing are only constrained by design rules. Even when targetting sea-of-gates masters, the basic blocks (e.g., transistors or transistor pairs) on such masters are often highly symmetrical (often 4-way, sometimes even 8-way [GrSt94]). Thus the orientation of the datapath, and the directions for bit-slice stacking and signal flow area are usually only determined by external pin-constraints and independent of the base substrate.

Figure 2.12: Extents of datapaths and modules

#### Suitable FPGA Architectures

In stark contrast, any kind of layout on FPGAs has to take the fixed underlying architecture of the FPGA chip into account. The freedom for specifying an FPGA architecture is highly limited by the large amount of chip area consumed for implementing the programming facilities for logic and routing (see [BFRV92]). For this reason, symmetrical blocks are quite rare for FPGAs and do not exceed 4-way symmetry even when they are actually implemented [Atme94], [Algo92].

When designing any kind of physical design software for FPGAs, the composition of the logic blocks and the structure of the routing network have to be considered carefully.

Since SDI aims at laying out regular circuits in a regular manner, it is directly influenced by the regularity of the underlying FPGA architecture. Thus, the architecture most suitable for our application would have highly regular and homogeneous logic blocks and routing resources.

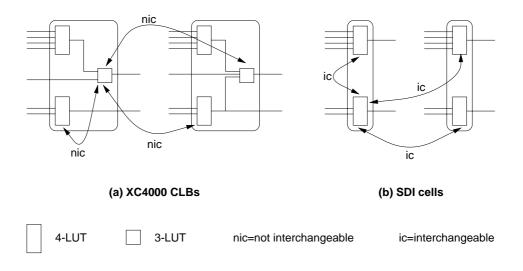

SDI does not depend on the core elements of the logic blocks (K-LUTs, MUXes). However, it relies on a regular logic-block structure. Single-output blocks, such as those found on Actel ACT [Acte95a], Xilinx XC6200 [Xili96b] are ideally suited to SDI. Coarse-grained multi-output blocks, such as AT&T ORCA [ATTM95], and Xilinx XC4000 CLBs, can be decomposed into regular single-output blocks (Section 2.7.3). However, this becomes difficult for fine-grained multi-output blocks such as QuickLogic pASIC2 [Quic95] or Atmel AT6000 [Atme94]. Here, a library-based technology mapping could assemble the multi-output blocks, each of which would then be placed as a unit. Architectures that directly couple logic-block functionality to placement locations, e.g., Pilkington/Motorola TS-series tiles [Pmel96], would have to carefully trade-off placement regularity vs. wasted space due to partially filled tiles. They could be better exploited using hierarchical clustering placement methods.

FPGAs with a row-oriented topology often lack the routing resources for two orthogonal signal flows. Architectures with sets of tightly interconnected

logic-blocks and hierarchical routing, such as the Altera FLEX10K series [Alte95], are better exploited by clustering placement methods [CuoL96] than by our regular-array approach. Applying our methods to chips with routing through a universal interconnection matrix would not yield much of an improvement: these FPGAs dedicate much of their die area to the cross-bar switch, which provides an almost constant-delay routing independent of circuit placement [ACCK96]. However, with an increasing number of logic blocks the size of the cross-bar (even if not fully populated) consumes too much area to be practical for all but highly specialized applications. Thus, our requirements are currently best fulfilled by matrix-structured FPGAs.

We chose to target the Xilinx XC4000 family, since it provides a homogeneous routing structure (matrix) as well as logic-blocks that are easily regularized. The recent XC6200 family, which was not available in time to be included in our research, would also fulfill the criteria. Due to the fine logicblock granularity, it would also be less dependent on the compaction step (Section 2.6).

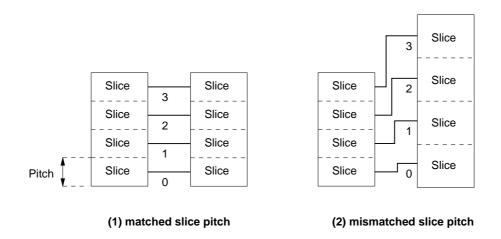

#### **Bit-Slice Pitch**

As with full-custom and macro-cell-based datapaths, a fourth quantity becomes relevant when aiming for a regular layout. The *pitch* of a bit-slice is the height of a single slice (Figure 2.13). For a regular layout, all bit-slices in modules in a datapath should balance the pitch. Otherwise, routing becomes more difficult and congestion increases (Figure 2.13.(2)). This becomes especially critical on FPGAs, where the channel width is fixed on the die and signals are delayed by the programmable routing elements.

Figure 2.13: Matched and mismatched bit-slice pitch

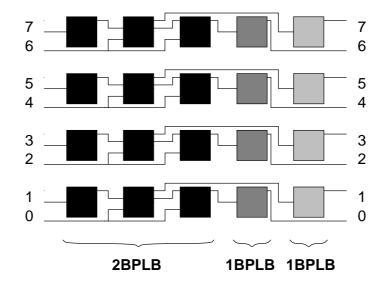

However, for FPGAs, it is useful to extend the classical concepts of bit-slice and pitch to accomodate the coarse granularity of logic blocks compared to full-custom/macro-cell, or even gate arrays and sea-of-gates. Since LBs often have multiple outputs, even a slice having only the height of single LB can conceivably compute multiple different functions at once. Thus, this minimal slice can process more than a single bit.

In a similar manner, we extend the concept of pitch from the simple height measure of a bit-slice to the number of bits with different significances actually processed per LB height  $(BPLB)^3$ .

**Explanation 3** *Bits per logic-block-height* (BPLB) is a bit-slice specific quantity. It is defined as the number of outputs with different bit significances on a given bit-slice divided by the height of this bit-slice in logic blocks.

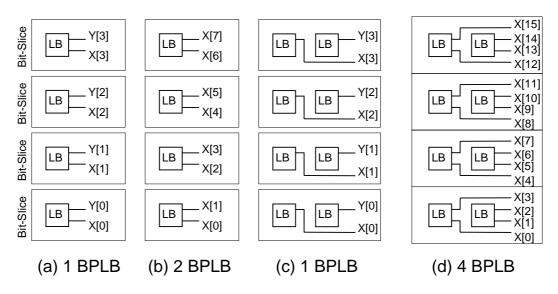

Figure 2.14 gives some examples for different BPLB values. It assumes LBs with two independent inputs (as on the XC4000, Section 2.1.1). E.g., in Figure 2.14.a each bit-slice is one LB high and has two outputs, but both with the same significance. Since multiple outputs with the same bit-significance do not influence the BPLB, (a) processes 1 BPLB. Furthermore, with a long bit-slice that contains multiple LBs in a single row, the BPLB value can exceed the number of independent outputs of a LB (Figure 2.14.d). As with pitch, BPLB should stay as constant as possible across an entire datapath for maximal performance.

Figure 2.14: Examples for BPLB values

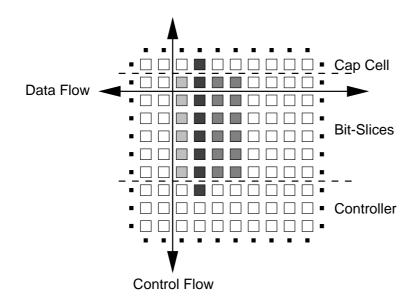

Applying these concepts to our concrete target FPGA family, the Xilinx XC4000 series of chips, we determine the following specifics: The dataflow of the hard-carry logic (Section 2.1) requires a vertical stacking of bit-slices inside a module, with the LSB at the bottom and the MSB at the top. The modules themselves will be placed horizontally, leading to a topology as shown in Figure 2.15. The orthogonal signal flows can be efficiently implemented in this arrangement: The (possibly high fan-out) control signals are efficiently routed on VLLs, while data signals mainly use the various horizontal routing resources. By using VLLs, control signals can be distributed with minimum

<sup>&</sup>lt;sup>3</sup> Previous papers refer to this quantity as bits-per-CLB BPC

skew along the entire height of the chip, making them easily accessible to all bit-slices in a module.

## 2.3.2 Chip Topology

After establishing the topology for the datapath itself, we now have to determine where to place it on the chip. This is most critical for FPGA-based systems with a fixed pin-out (like the Sparxil-processor [KoGo94]). When the pin-out of the FPGA can remain variable (e.g., when a system-wide programmable routing network based on FPICs is employed), the chip pin-out itself can be adjusted to accomodate a floating placement of the datapath section of the whole circuit.

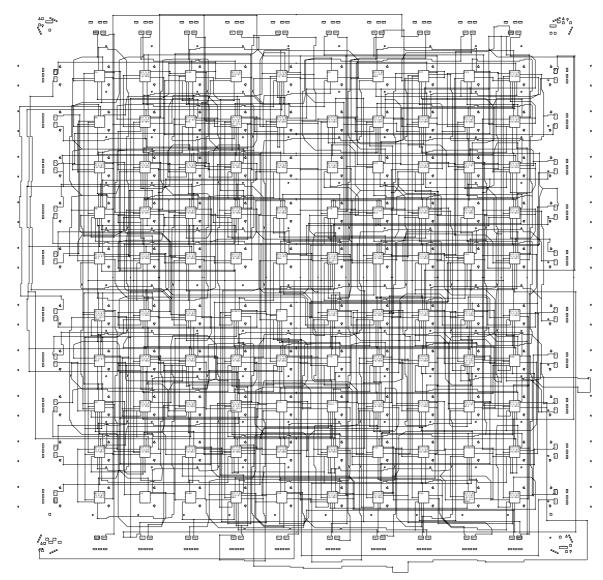

Figure 2.15: On-chip topology

The chip topology targeted by SDI is characterized by a fixed threepartite layout (Figure 2.15). The large middle section holds the regular part of the datapath. This part consists of the horizontal arrangement of modules, each composed of vertically stacked bit-slices. The area below the datapath is intended to hold the controller, whose irregular logic is not processed by SDI. A small area above the regular section can hold irregularities in the modules such as *cap cells*, e.g., the processing of overflow and carry bits in a signed adder. Such irregularities may also reach below the datapath baseline into the controller section, e.g., the initialization of the carry chain below the LSB of the adder mentioned above. After datapath placement, all of the remaining chip area may be used for implementing the controller through conventional methods (the XACT tool suite for Xilinx FPGAs).

The dimensions of the three areas are application-specific and must be manually designated by the user. In the case of FPGAs with a fixed pin-out on a printed circuit board (PCB), the area heights are primarily determined by the interconnection pattern on the PCB, which in turn depends on the width requirements for external busses.