8. E.I.S.-Workshop am 8. und 9. April 1997 an der Universität Hamburg

# Entwurf eines Digital-Audio-Receiver als Praktikumsaufgabe

Peter Blinzer

Technische Universität Braunschweig

Abteilung Entwurf integrierter Schaltungen (E.I.S.)

Postfach 3329, Gaußstraße 11, 38023 Braunschweig

Telefon: 0531-391-2380, Fax: 0531-391-5840

Email: blinzer@eis.cs.tu-bs.de

## Zusammenfassung

Der Beitrag behandelt die Verwendung einer Entwurfsaufgabe mit Bezug zur Unterhaltungselektronik in einem Chip-Entwurfspraktikum. Innerhalb eines Semesters wurde von Studenten eine Schaltung für Empfang und Dekodierung eines Digital-Audio-Signals als Verilog-Modell beschrieben und in einem FPGA implementiert. Die Aufgabe erlaubte die praktische Anwendung einer elementaren Entwurfsmethode an einem nichttrivialen Problem und war sehr motivierend für die Teilnehmer, nicht zuletzt weil der Test in einer Hardwareumgebung einen Entwurfserfolg hörbar werden ließ.

## 1 Einführung

Praktika sind ein wichtiges Element im Bereich der akademischen Ausbildung zum Entwurf von integrierten Schaltungen. Vorlesungen sind zwar durchaus ausreichend, um eine gute theoretische Grundlage in diesem Gebiet zu schaffen, aber leider erlauben sie es nicht, reale Erfahrungen in der Anwendung von Methoden und Werkzeugen für den Chip-Entwurf zu gewinnen. Durch eine Kombination von Vorlesungen mit Entwurfspraktika können sich Theorie und Praxis gegenseitig ergänzen. Insbesondere kann dabei auch direkt anwendbares Wissen im Bereich des Schaltungsentwurfs vermittelt werden.

Die Entwurfsaufgabe eines Praktikums muß verschiedenen Anforderungen gerecht werden.

Zu den wichtigsten Anforderungen gehört dabei die praktische Anwendbarkeit einer gelehnten Entwurfsmethodik. Der zur Lösung der Aufgabe erforderliche Entwurfsaufwand spielt ebenso eine große Rolle, denn schließlich steht nur eine recht begrenzte Praktikumszeit zur Verfügung. Die Motivation, welche eine Aufgabe für die Studenten mit sich bringt, ist ein weiterer Punkt, der nicht vernachlässigt werden darf, denn nur bei geeigneter Motivation werden vorhandene kreative Fähigkeiten freigesetzt. Natürlich gilt es auch andere Dinge zu beachten, die genannten besitzen aber eine Schlüsselrolle für den Erfolg eines Entwurfspraktikums.

Die Ausbildung zum Chip-Entwurf besteht an der Braunschweiger Abteilung E.I.S. zur Zeit aus zwei Vorlesungen und diese begleitende Praktika. Im Sommersemester 1996 wurde im Entwurfspraktikum für FPGAs eine Aufgabe mit Bezug zur Unterhaltungselektronik gestellt. Die Studenten sollten eine Interface-Schaltung entwickeln, welche das von einem normalen Audio-CD-Player ausgegebene Digital-Audio-Signal dekodiert und für die akustische Wiedergabe über einen Digital-Analog-Converter (DAC) vorverarbeitet.

Diese Aufgabe erwies sich als gut geeignet, um den Entwurf einer integrierten Schaltung mit HDL-Modellierung und Schematic-Entry zu üben. Alle Teilnehmer beteiligten sich mit einem sehr beachtlichen Eifer und lösten die gestellte Entwurfsaufgabe erfolgreich in Gruppen zu je drei Studenten.

## 2 Aufbau des Entwurfspraktikums

Das FPGA-Entwurfspraktikum erstreckte sich im Sommersemester 1996 über insgesamt 12 Wochen. Voraussetzung für die Teilnahme an dem Praktikum waren Vorkenntnisse über die verwendeten CAD-Werkzeuge, welche in CAD-Übungen des vorangegangenen Wintersemesters erworben werden konnten. Kenntnisse über die Hardwarebeschreibungssprache Verilog und das Entwurfssystem Powerview waren daher bereits vorhanden.

In jeder Woche standen den Teilnehmern des Praktikums zwei Termine zu je 90 Minuten an CAD-Workstations zur Verfügung. Diese Zeit erwies sich als gerade ausreichend zur Lösung der Aufgabe. Eine vergleichbare Zeit wurde für die Planungsarbeiten und das Schreiben einer Projektdokumentation veranschlagt.

Die Beschreibung des Entwurfsproblems wurde bereits gegen Ende des Wintersemesters ausgegeben. Die Studenten konnten sich daher in den Semesterferien mit ihrer Aufgabe vertraut machen und so mögliche Verständnisprobleme frühzeitig erkennen. Die Beschreibung enthielt neben den Anforderungen an den Entwurf die Spezifikation des Digital-Audio-Standards [1] und die Skizzierung eines Lösungsansatzes.

Das Praktikum bestand aus insgesamt fünf einzelnen Phasen (Bild 1). Diese Phasen wurden jeweils durch die Abgabe bestimmter Zwischenergebnisse abgeschlossen, welche nach ihrer Überprüfung im Rahmen von Kolloquien mit den einzelnen Gruppen besprochen wurden.

| Woche | Phase | Entwurfsziel          |

|-------|-------|-----------------------|

| 1     |       |                       |

| 2     | I     | Verilog-Modell        |

| 3     |       |                       |

| 4     | II    | Schematics (komplett) |

| 5     |       |                       |

| 6     |       |                       |

| 7     | III   | Schematics (korrekt)  |

| 8     |       |                       |

| 9     |       |                       |

| 10    | IV    | FPGA -Konfiguration   |

| 11    |       |                       |

| 12    | V     | Projektdokumentation  |

Bild 1: Ablauf des Praktikums

Jede der fünf Entwurfsphasen deckte bestimmte Teile des gesamten Entwurfsablaufs ab. Ihre Grenzen untereinander stellten daher nicht nur günstige Kontrollpunkte für den Betreuer und die Studenten dar, sondern sie hoben auch die Zeitpunkte wichtiger Entwurfsentscheidungen hervor.

In der ersten Phase des Praktikums, welche drei Wochen umfaßte, war ein simulierbares Modell in der Hardwarebeschreibungssprache Verilog zu schreiben. Dieses sollte auf Register-Transfer-Ebene arbeiten und ein vollsynchrone Takschema verwenden. Ein Testrahmen für die Simulation und Überprüfung dieses Modells wurde zur Verfügung gestellt. Einige Teile der rechnergestützten Entwurfsarbeiten wurden von den meisten Studenten in dieser Phase auch an ihren eigenen Heim-PCs erledigt, wobei sie die frei kopierbare Version des Verilog-Simulators VeriWell [2] verwendeten. Für den Abschluß dieser Phase mußte das Verilog-Modell einen Datensatz aus mehreren Audio-Datenblöcken im gestellten Testrahmen korrekt verarbeiten. Eine Dokumentation des Verilog-Modells im Bezug auf Funktion, Modulstruktur und Schnittstellen wurde ebenfalls verlangt.

Die zweite Praktikumsphase dauerte zwei Wochen. In dieser Zeit sollte das Verilog-Modell vollständig in Schematics umgesetzt werden. Es wurde allerdings nicht verlangt, daß diese bereits perfekt und fehlerfrei waren. Die Schematics sollten jedoch die Fähigkeit einer Gruppe zeigen, das eigene Verilog-Register-Transfer-Modell in eine Schematic-Darstellung zu transferieren. Die Hierarchie der Schematics sollte daher mit der des Verilog-Modells möglichst übereinstimmen und lediglich weiter verfeinert werden. Zu den Schematics wurde eine Dokumentation verlangt, welche Hierarchie, Modulstruktur, Funktionen und Schnittstellen erläuterte.

In der dritten Phase des Praktikums wurden die Schematics mittels Simulation getestet und gegebenenfalls korrigiert. Die für diese Phase vorgesehene Zeit betrug dreieinhalf Wochen. In dieser Zeit waren für alle nichttrivialen Teile der Schaltung Tests für die beabsichtigte Funktion zu entwickeln und zu dokumentieren.

Wie schon in der ersten Phase wurde auch hier ein Testrahmen für die vollständige Schaltung zur Verfügung gestellt. Für das Verilog-Modell entwickelte Testdaten konnten mit diesem Testrahmen wiederverwendet werden. Als Abschluß dieser Phase hatte der Schematic-Entwurf daher auch dieselben Testdaten zu verarbeiten, die schon in der ersten Phase für den Verilog-Test verwendet worden waren.

In der vierten Phase hatten die Praktikumsguppen weitere zweieinhalb Wochen Zeit für die Optimierung der bereits funktional korrekten Entwürfe. Ziel dieser Optimierungen war es, die Schaltung auf einem bestimmten FPGA-Typ zu implementieren, der sowohl im Bezug auf die vorhandenen Logikressourcen als auch auf die Schaltgeschwindigkeit sehr beschränkt ist. In dieser Phase mußte daher auch die Plazierung und Verdrahtung der Schaltung mit der XACT-Software von Xilinx vorgenommen werden. Das Programm Paket war in den CAD-Übungen des vorangegangenen Wintersemesters jedoch nicht verwendet worden und daher völlig neu für die Studenten. Eine relativ kurze Vorstellung reichte aber erfreulicherweise aus, um die Ausführung aller benötigten Arbeitsschritte zu vermitteln. Die in dieser Entwurfsphase vorgenommenen Optimierungen bestanden im wesentlichen aus der Entfernung redundanter Logik, Pipelining und der Verwendung von „one hot encoding“-Zustandskodierungen in zeitkritischen Zählern und Zustandsautomaten. Die Phase wurde durch eine Postlayout-Simulation des plazierten und verdrahteten Entwurfs abgeschlossen. Neben den FPGA-Konfigurationsdaten wurde auch eine kurze Dokumentation über die in dieser Phase angewandten Optimierungen angefertigt.

In der letzten Praktikumswoche schließlich, der Abschlußphase des Praktikums, wurde von den einzelnen Gruppen jeweils eine vollständige Projektdokumentation zusammengestellt. Diese basierte auf den vier Phasendokumenten, die im Laufe des Praktikums entstanden waren. Eine Besprechung dieses Dokumentes fand in dem Abschlußkolloquium statt, in welchem auch ein Test der entstandenen Schaltung in einer realen Testumgebung für den FPGA-Chip stattfand. Das Testergebnis war hierbei hörbar.

### 3 Die Entwurfsaufgabe

Die Aufgabe des FPGA-Praktikums bestand in der Entwicklung einer Interface-Schaltung für ein Digital-Audio-Signal auf einem Xilinx-FPGA des Typs 3042-70 [3]. Der Baustein war für diese Aufgabe gerade ausreichend, wie ein Entwurfsprototyp gezeigt hatte.

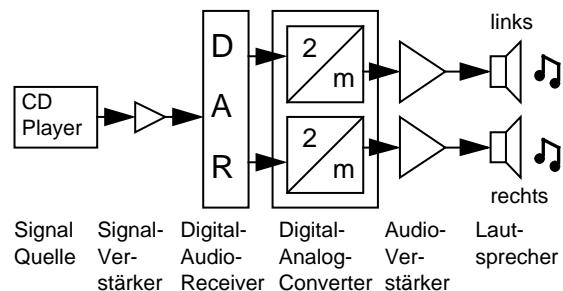

Als Signalquelle wurde ein handelsüblicher Audio-CD-Player verwendet, der ein Digital-Audio-Signal nach dem Standard SPDIF [4] von Sony und Philips ausgab. Dieses serielle Signal wurde in der Testschaltung mit einem Verstärker von seinem  $\pm 200\text{mV}$ -Pegel auf  $0\text{V}/5\text{V}$  gebracht und danach in das FPGA gespeist. Es war hierbei immer noch biphasen-codiert und besaß eine Bitrate von  $5.6\text{Mbit/s}$ . Für den Empfang dieses Signals wurde allerdings kein Taktregenerator auf PLL-Basis verwendet, sondern das FPGA wurde mit einer Frequenz von  $16\text{MHz}$  getaktet. Hierdurch konnte es eine Signalabtastung mit etwa drei Abtastwerten pro Codebit vornehmen und das Signal auf der Grundlage der Biphasen-Codierung wieder in einen dekodierten Bitstrom umsetzen. Dieser Prozeß war der aufwendigste und zeitkritischste Teil des Entwurfs, weswegen das Entwurfsprojekt auch seine Bezeichnung „Digital-Audio-Receiver“ (DAR) bekam. Nach Rekonstruktion der 32-Bit SPDIF-Datenblöcke und Auswertung der Kontrolldaten wurden die Audio-Daten schließlich seriell an den Stereo-Digital-Analog-Converter der Testschaltung übertragen. Die Ausgänge des DAC waren über Audio-Verstärker mit Lautsprechern verbunden, so daß die Ausgaben des FPGAs hörbar waren. Bild 2 zeigt ein vereinfachtes Systemdiagramm der verwendeten Testschaltung.

Bild 2: DAR-Testschaltung

Eine Grundvoraussetzung für die erfolgreiche Bearbeitung der Aufgabe war das Verstehen der digitalen Audio-Übertragung entsprechend des SPDIF-Standards. Die Kommunikation erfolgt hierbei unidirektional und selbstdidakktisch über ein einfaches Koaxialkabel oder eine Glasfaser.

Die Übertragung sowohl der Daten als auch des Datentaktes im SPDIF-Signal erfolgt durch eine Codierung der zu übertragenden Daten mit dem Biphasen-Code. Bei dieser Codierung wird jedes Datenbit durch zwei Codebits dargestellt, wobei eine logische Null durch eine Folge von zwei gleichen Bits (00 oder 11) repräsentiert wird und eine logische Eins durch eine Folge von zwei ungleichen Bits (01 oder 10). Dabei wird die Codierung so gewählt, daß zwischen zwei codierten Datenbits immer eine Flanke im SPDIF-Signal auftritt. Die Rückgewinnung von Daten und Datentakt erfolgt ausschließlich durch die Beobachtung und die Abstandsmessung der Signalflanken. Aufgrund der Tatsache, daß nur drei Übertragungsraten für die Codebits möglich sind, die außerdem von der Abtastungsfrequenz der Audio-Daten abhängen, ist die Dekodierung relativ unproblematisch.

Im Fall von Audio-CDs werden die Audio-Daten durch 16-Bit Abtastung mit 44,1kHz auf zwei Audio-Kanälen gewonnen. Die einzelnen Abtastwerte werden danach in je einen 32-Bit SPDIF-Datenblock verpackt, so daß sich als Übertragungsrates der Codebits  $44100 \cdot 2 \cdot 32 \cdot 2 = 5.644.800$  Bit/s ergibt. Neben 44,1Khz sind noch zwei weitere Audio-Abtastfrequenzen als Basis für SPDIF-Signale möglich, nämlich 48kHz bei Digital-Audio-Tapes (DAT) und 32Khz beim Digital-Audio-Broadcasting (DAB). Bei der Konstruktion des Digital-Audio-Receivers war jedoch nur die CD-Datenrate zu betrachten.

Die einzelnen Datenblöcke beginnen in der Übertragung mit speziellen Präambel-Codes, die nicht mittels des Biphasen-Codierungsschemas entstehen können und so die Synchronisation von Blockgrenzen und Bitgrenzen erlauben. Während des Empfangs eines Datenblockes war die Bitsynchronisation dennoch ständig durch die Schaltung zu aktualisieren, da das Verhältnis von Taktfrequenz zur Codebitrate zu durchschnittlich 2,8 Abtastungen pro Codebit führte.

Durch die Präambel-Codes wird aber nicht nur ein Blockanfang markiert, sondern neben der Zuordnung eines Datenblocks zu einem der zwei Stereo-Kanäle auch die Gruppierung in „Frames“ aus 192 Blockpaaren vorgenommen. Aufgrund all dieser Randbedingungen gestaltete sich der Empfang des Digital-Audio-Signals als der schwierigste Teil des gesamten Entwurfs.

Nach der Dekodierung des Digital-Audio-Bitstroms war die Rekonstruktion der SPDIF-Datenblöcke vergleichsweise unkompliziert. Die Amplitudenwerte für die Audio-Wiedergabe konnten aus diesen Blöcken direkt abgegriffen werden. Bestimmte Statusdaten waren abhängig von der jeweiligen Blockpaarnummer in einem Frame ebenfalls zu extrahieren und auszuwerten, um die Gültigkeit und Wiedergabefähigkeit des Signals sicherzustellen.

Die Audio-Amplitudenwerte wurden zum Abschluß seriell an einen AD8522 Stereo-DAC [5] übertragen. Dieser DAC besitzt lediglich eine Auflösung von 12 Bit, weswegen die unteren vier Bit des Amplitudenwertes nicht verarbeitet werden konnten. In dem akustischen Umfeld des Testlabors, in dem die fertigen Entwürfe getestet wurden, war dieser Informationsverlust jedoch kaum wahrnehmbar.

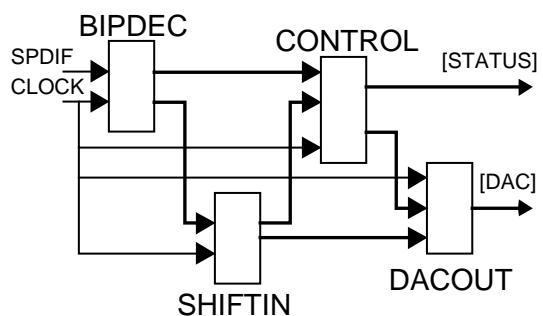

Um den Entwurf nicht zu kompliziert und fehleranfällig zu machen, wurden den Studenten in der Aufgabe Hinweise für einen möglichen Lösungsansatz gegeben, welche auf einem schon erfolgreich fertiggestellten Prototypen basierten. Diese schlossen ein Diagramm der Grobstruktur ein (Bild 3). Die Funktion der einzelnen Module wurde dabei nur relativ abstrakt beschrieben, um den Entwurf nur anzuleiten und nicht zu steuern.

Bild 3: Grobstruktur des DAR

Das Modul BIPDEC wurde daher lediglich als SPDIF-Empfänger auf Bitebene charakterisiert, welcher neben Biphasen-Dekodierung und Bitsynchronisation auch die Präambel-Detektion vornimmt. Die Zusammensetzung der SPDIF-Datenblöcke wurde SHIFTIN zugeordnet, einem Schieberegister mit Synchronisationssteuerung, serielllem Eingang und parallelem Ausgang. Die Sammlung und Auswertung der Statusdaten wurde in CONTROL zusammengefaßt, während die Ausgabe von Daten an den DAC schließlich von DACOUT durchgeführt wurde.

## 4 Besonderheiten des Entwurfs

Die Entwurfsaufgabe zeichnet sich durch einige Besonderheiten aus, die sie für ein Praktikum nicht nur gut geeignet machen, sondern die auch eine gewisse Herausforderung für die Studenten mit sich bringen.

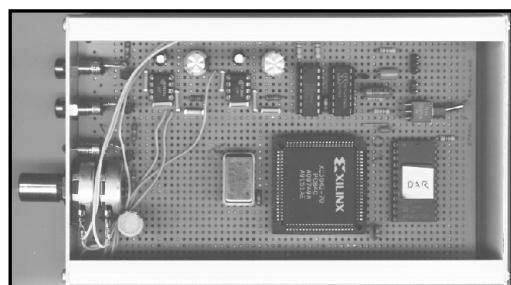

So besitzt der benutzte FPGA-Typ (3042-70) sehr knapp bemessene Logikressourcen und nur eine relativ geringe Schaltgeschwindigkeit. Am Prototypenentwurf (Bild 4) ist erkennbar, daß das FPGA mit einem DAR zu etwa 80% ausgelastet ist, wobei jedoch noch keine Probleme bei der Plazierung und Verdrahtung auftreten. Innerhalb eines Taktes können des weiteren nur 2 CLBs von einem Signal durchlaufen werden. Es war daher bei der Optimierung jeweils abzuwegen, welche Art der Optimierung notwendig, möglich und effektiv ist.

Bild 4: Layout des DAR-Prototyps

Insbesondere die Anwendung von serieller und paralleler Verarbeitung, von Pipelining und von „one hot encoding“ wurde hierbei erfolgreich zur Optimierung eingesetzt. Aufgrund der FPGA-Beschränkungen waren letztlich alle Gruppen gezwungen, gewisse Änderungen an ihren Entwürfen vorzunehmen. Hierdurch wurde den Studenten deutlich, daß ein Entwurfsweg oft auch Iterationen beinhaltet und mehr als nur eine korrekte Lösung existiert.

Da keine Vorgaben für die Verarbeitungszeit innerhalb des FPGAs bestanden und die FPGA-Architektur Pipeline-Optimierungen nahezu ohne Zusatzkosten bezüglich Logikressourcen erlaubte, existierten weit mehr Möglichkeiten zur Schaltungsoptimierung, als wirklich benötigt wurden. Die resultierenden Entwürfe nutzten die vorhandenen CLB-Ressourcen des FPGAs mit Auslastungen zwischen 70% und 90% mehr als gut aus, wofür im wesentlichen die Verwendung serieller Verarbeitung und Pipelines Ursache ist.

Mit Ausnahme des abschließenden Tests in der Hardwareumgebung (Bild 5) wurden alle sonstigen Tests des Digital-Audio-Receiver mit Simulationen vorgenommen. Zu den gestellten Testrahmen für das Verilog-Modell und die Schematic-Implementierung waren hierbei von den Studenten Testdatensätze zu entwickeln und anzuwenden, welche die Funktionsprüfung ihrer eigenen Schaltungen erlaubten. Lediglich ein Testdatensatz für den vollständigen Entwurf war vorgegeben, so daß weder Entwicklung noch Durchführung von Tests in diesem Praktikum vernachlässigbar waren. Aufgrund dieser Teststrategie war der Entwurfsablauf vergleichbar zu dem eines maskenprogrammierbaren ASICs.

Bild 5: Hardwareumgebung des DAR

Die in dem Praktikum gesammelten Erfahrungen stellen damit eine gute Basis für die Lösung von Entwurfsproblemen in der Praxis dar, bei denen aufgrund der Komplexität und der Kosten ein „erprobieren“ einer Schaltung undurchführbar ist, sondern eine „first time right“-Arbeitweise notwendig ist.

## 5 Ergebnisse

Im Sommersemester 1996 nahmen 15 Studenten am FPGA-Entwurfslabor teil, die in 5 Gruppen zu je drei Studenten arbeiteten. Jede der fünf Gruppen bestand das Praktikum erfolgreich, da alle fünf angefertigten Entwürfe die geforderte Post-Layout-Simulation bestanden. Drei dieser Entwürfe arbeiteten auch in der Testschaltung auf Anhieb problemlos, während die übrigen zwei die Klänge leicht gestört wiedergaben. Die Störungen hatten ihre Ursache in einer nicht sehr zuverlässig arbeitenden Bitsynchronisation, die zu Datenverlusten beim Empfang führte. Dieses Problem war durch die verwendeten Testdaten nicht entdeckt worden. Mit leichten Korrekturen wurden schließlich auch diese Entwürfe real voll funktionsfähig.

Eine abschließende Befragung der Studenten ergab, daß alle das Praktikum weiterempfehlen würden, obwohl es sehr viel Arbeit erforderte. Die Art der Entwurfsaufgabe wurde als äußerst motivierend empfunden, da die vielfach benutzte Technik der Tonübertragung auf digitalen Weg durchschaubar gemacht wurde und das hörbare Ergebnis die Verbindung zur erlebten Realität herstellte.

## 6 Zusammenfassung

Der Entwurf des Digital-Audio-Receiver wurde trotz der Komplexität erfolgreich in unserem FPGA-Praktikum als Aufgabe verwendet. Die Aufgabe ermöglichte nicht nur die praktische Anwendung einer Entwurfsmethodik, sondern sie erwies sich auch als sehr motivierend für die Studenten. Es konnten dabei sowohl alternative Lösungen für ein Problem angewendet werden, als auch die Funktionsfähigkeit unter realen Randbedingungen überprüft werden.

## Literaturverzeichnis

- [1] International standard IEC958, digital audio interface, First edition 1989-03.

- [2] Wellspring Solutions, VeriWell™ User's Guide 2.0, June, 1995.

(verfügbar bei <http://www.wellspring.com>)

- [3] Xilinx, The Programmable Logic Data Book, 1994

- [4] Francis Rumsey, John Watkinson, The Digital Interface Handbook, Focal Press 1993

- [5] Analog Devices, AD8522 Data Sheet, 1994