Für die abstrakte Kommunikations-Modellierung wurden mit GreenBus und der auch daraus hervorgehenden TLM-2.0 große Erfolge in der Standardisierung der TLM erzielt. Für weniger abstrakte Modellierung existiert so ein Standard noch nicht. Da TLM tendenziell eine abstrakte Modellierung sein soll, drängt sich jedoch die Frage auf, ob weniger abstrakte oder gar taktgenaue TLM überhaupt notwendig ist. Dafür sollen hier die zwei wichtigsten Gründe angeführt werden.

Erstens kann es sich bei einer abstrakten Systemmodellierung und -analyse herausstellen, dass es für eine bestimmte Hardware-Komponente keinen fertigen IP-Block gibt, so dass dieser neu entwickelt werden muss. Ausgehend vom vorhandenen abstrakten Modell wird dann der fehlende Block schrittweise solange verfeinert, bis eine klassische Hardware-Synthese möglich ist. Diese Synthese-Vorgabe ist natürlich deutlich weniger abstrakt, im schlimmsten Falle entspricht sie dem Register-Transfer-Level. Die Überführung der am wenigsten abstrakten, noch standardisierten TLM-Darstellung in eine synthetisierbare ist in einem Schritt für nicht-triviale Funktionsblöcke kaum machbar. Das Verlassen der TLM-Welt, also der Übergang von relativ einfachen Schnittstellen hin zu RTL-Schnittstellen mit hunderten von Signalen sollte aber möglichst spät im Entwurf passieren, nur leider gibt es keinen weniger abstrakten TLM-Standard. Der Entwickler muss entweder zwei wahrscheinlich verschiedene TLM-Modellierungen beherrschen (die standardisierte abstrakte und eine proprietäre taktgenaue), oder das Modell muss an einen Experten für die taktgenaue Modellierung übergeben werden. Der erste Fall stellt eine große Belastung des Entwicklers dar, insbesondere wenn bei der taktgenauen TLM wieder mehrere grundverschiedene proprietäre TLM-Schnittstellen existieren. Der zweite Fall ist teuer und birgt das Risiko von Missverständnissen, die bei der Übergabe der Modelle passieren.

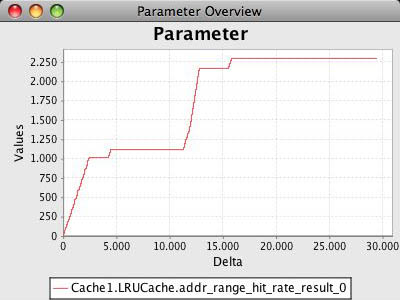

Der zweite Hauptgrund für den Bedarf an taktgenauem TLM besteht darin, dass die Ergebnisse einer abstrakten TLM-Simulation für diverse Fragestellungen nicht ausreichen. Während im abstrakten Modell die Aussage genügen mag: „Circa 100 MHz liefern eine ausreichende Antwortzeit“, kann beispielsweise bei einem mobilen Gerät die Entscheidung zwischen 95 oder 100 MHz den entscheidenden Marktvorteil einer längeren Akkulaufzeit bedeuten. Dann benötigt man eine präzise Aussage, ob 95 MHz ausreichen. Während solche Vorhersagen mit Register-Transfer-Modellen berechnet werden können, ist die Performance solcher RTL-Simulationen im Vergleich zur abstrakten TLM sehr gering. Ideal wäre daher ein abstraktes TLM-Modell, das trotzdem wesentliche Aussagen des präzisen RTL-Modells effizient liefert.

Taktgenaue TLM ist folglich notwendig. Gäbe es dafür einen Standard, würden sich für die IP- und Werkzeughersteller Aufwand und Kosten reduzieren, da nicht eine Vielzahl von proprietären taktgenauen „Standards“ unterstützt werden müssen. Falls ein solcher bisher fehlender Standard für taktgenaues TLM darüber hinaus auf den Mechanismen des vorhandenen abstrakten Standards TLM-2.0 aufbauen würde, falls also die Standards nahe beieinander liegen würden, müssten Entwickler nur wenig hinzulernen, um sowohl abstrakt als auch taktgenau modellieren zu können.

Aus diesem Grund forschten wir an einem Vorschlag für ein Standard-Interface für taktgenaue TLM von Funktionsblöcken und Kommunikationsstrukturen mit memory-mapped Bus-Interfaces in Analogie zum vorhandenen TLM-2.0. Wie erwähnt sollte ein taktgenaues TLM-Modell möglichst viel abstrahieren und immer noch gewünschte Aussagen liefern. Beides musste präzisierbar sein: Wovon wird abstrahiert? Welche Aussagen sind trotzdem möglich? Daher haben wir die taktgenaue TLM-Simulation genauer untersucht und Möglichkeiten zur Abstraktion gefunden, die die Taktgenauigkeit der gewünschten Simulationsaussagen nicht gefährden.

Bei unserem Vorschlag für einen taktgenauen TLM-Standard wurde nachgewiesen, dass die bereits in TLM-2.0 vorhandenen Mechanismen im Wesentlichen ausreichen, jedoch wurden einige Erweiterungen und Änderungen von TLM-2.0 nötig. Neben diesen generischen Änderungen von TLM-2.0 wurden auch Regeln bestimmt, wie spezielle memory-mapped Bus-Interfaces auf den um Taktgenauigkeit erweiterten TLM-2.0-Standard abgebildet werden können. Zusätzlich haben wir auch noch untersucht, wie der verwendete SystemC-Simulator für taktgenaue Modelle wesentlich optimiert werden kann.

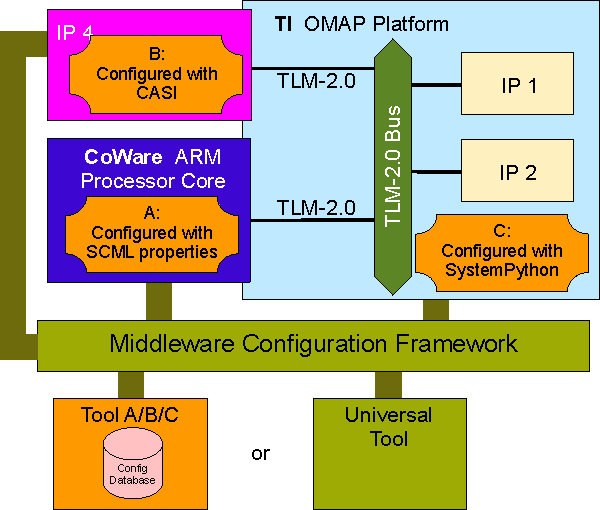

Nicht zuletzt auch aufgrund unserer Expertise im Bereich der taktgenauen Modellierung war die Abteilung E.I.S. im Rahmen unserer Mitarbeit in der Open-Source-Initiative GreenSocs auch in die OCP-IP (Open Core Protocol - International Partnership) eingebunden. Gemeinsam mit CoWare, Nokia, Sonics und Texas Instruments arbeiteten wir in der System-Level-Design Working-Group und haben dazu beigetragen, die SystemC-Implementierung der OCP-TLM-Kanäle zu verbessern und neuartige, GreenBus-basierte OCP-TLM-Kanäle zu entwickeln und zu untersuchen. Die GreenSocs-Initiative wurde in 2007 mit dem Titel "OCP-IP Contributor of the Year" ausgezeichnet.

Mit Hilfe der Ergebnisse der oben genannten Untersuchungen wurde das OCP-TLM-Paket komplett auf den neuen TLM-2.0 Standard umgestellt. Die Möglichkeit, mit diesen neuen OCP-TLM-Kanälen taktgenaue TLM-Modelle zu erstellen, geht weit über den Rahmen des TLM-2.0-Standards hinaus, welcher ursprünglich für höhere Abstraktionsebenen entworfen wurde. Damit wurden unsere Forschungsergebnisse bezüglich taktgenauer TLM in industriellem Umfeld erprobt und angewendet. |