Entwicklung eines

RISC-Prozessors

als Beispiel für einen großen Semi-Custom-Entwurf

(Kooperation mit der Fa. LSI LOGIC)

(P.Blinzer, E. Cochlovius, M. Schäfers, K.-P. Wachsmann, bis 1996)

Im Rahmen eines mehrjährigen Kooperationsvertrages mit der Firma LSI LOGIC GmbH wird die Methodik des Entwurfs großer Semi-Custom-Chips erforscht. Als Beispiel wurde der Entwurf des RISC-Prozessors TOOBSIE ausgewählt (TU Braunschweig Integrated Engine).

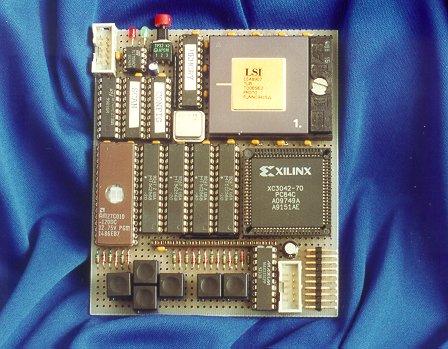

Bild 1: Der RISC-Prozessor TOOBSIE 2 auf einer Testplatine

Die Entwicklung eines ersten Prozessors TOOBSIE 1 und eines großen RISC-Prozessors TOOBSIE 2 wurden erfolgreich abgeschlossen. TOOBSIE 2 wurde mit einem eigens entwickelten Betriebssystem und diversen nichttrivialen Anwendungsprogrammen erfolgreich getestet (Bild 1). Folgende Unterprojekte wurden erfolgreich durchgeführt:

- Praktischer Entwurf eines RISC-Prozessors und Entwurfsmethodik

- Befehlssatz, Architektur, technische Merkmale und Performance-Analyse

- Einsatz von Hardware-Beschreibungssprachen

- Aufbau eines Evaluationssystems und Test des RISC-Prozessors

- Graphische Verifikation und Animation in frühen Entwurfsphasen mit STATEMATE

- Optimierung von Kontrolltransfer-Anweisungen (CTI)

- Entwicklung von Testmustern auf hohen Entwurfsebenen

Die wichtigsten Merkmale des Prozessors sind: 5-stufige Pipeline, 32-bit-breiter Datenpfad, Load-Store-Architektur, 32 Mehrzweckregister, nur ein Zyklus für die meisten Befehle, Drei-Adressformat, Delayed-Branch, Delayed-Load, Forwarding, On-Chip-Instruction-Cache mit RIB-Modus, Branch-Target-Instruction-Cache mit spekulativer Ausführung von Befehlen, durchschnittliche Ausführungszeit von 0,6 Zyklen für einen Branch, Kernel- und User-Modus, drei Interrupt-Ebenen, virtuelle Adressierung, synchrones oder asynchrones Busprotokoll, LSI-Gate-Array der Serie LCA 100k, brutto 106 000 Gatteräquivalente, 0.7µ-Sea-of-Gates-Technologie, CPI=0,99.

Das Projekt wurde in zwei deutschen und zwei englischsprachigen Lehr- und Arbeitsbüchern dokumentiert. Sie vermitteln sowohl Grundlagenwissen, vor allem auch zum Umgang mit Hardware-Beschreibungssprachen, als auch praxiserprobte Entwurfserfahrung.