# **Studienarbeit**

# Wavelet-Bildkompression auf dem adaptiven Rechner ACE-V

von cand. inform. Hagen Gädke

Abteilung Entwurf Integrierter Schaltungen (E.I.S.)

Prof. Dr. U. Golze

Betreuer: Dr. Andreas Koch

November 2003

# Erklärung

Ich erkläre, die vorliegende Arbeit selbständig und nur unter Benutzung der angegebenen Hilfsmittel angefertigt zu haben.

Hagen Gadke

Braunschweig, den 06.11.2003

# Inhaltsverzeichnis

| 1      | Einleitung                                         | 6  |

|--------|----------------------------------------------------|----|

| 2      | Anwendung und Entwurfsaspekte                      | 7  |

| 2.1    | Die diskrete Wavelet-Transformation                | 7  |

| 2.1.1  | Phase 1: mehrstufige Wavelet-Transformation        | 8  |

| 2.1.2  | Phase 2: Quantisierung                             | 11 |

| 2.1.3  | Phase 3: Lauflängencodierung                       | 12 |

| 2.1.4  | Phase 4: Huffman-Codierung                         | 13 |

| 2.2    | Die Software-Implementierung                       | 13 |

| 2.2.1  | Beschreibung der Software-Implementierung          | 13 |

| 2.2.2  | Effizienzsteigernde Implementierungs-Änderungen    | 15 |

| 2.3    | Definition der Anforderungen für die Studienarbeit | 16 |

| 2.4    | Partitionierung                                    | 16 |

| 3      | Der Software-Teil der Anwendung                    | 18 |

| 4      | Die Hardware-Software-Schnittstelle                | 21 |

| 4.1    | Slave-Mode-Zugriffe                                | 21 |

| 4.2    | Master-Mode-Zugriffe                               | 21 |

| 5      | Der Hardware-Teil der Anwendung                    | 23 |

| 5.1    | Pipelining                                         | 24 |

| 5.1.1  | Wavelet-Pipeline                                   | 24 |

| 5.1.2  | QZH-Pipeline                                       | 25 |

| 5.2    | Speicherorganisation                               | 28 |

| 5.2.1  | Speicherzugriffe während der Transformationen      | 28 |

| 5.2.2  | Aufteilung des Speichers für MARC                  | 35 |

| 5.3    | Stream-Flusskontrolle                              | 37 |

| 5.4    | Der Hardware-Teil im Überblick                     | 39 |

| 5.5    | Detaillierte Modulbeschreibungen                   | 42 |

| 5.5.1  | wavelet_8_4_1                                      | 42 |

| 5.5.2  | wavelet_16_2_hl                                    | 46 |

| 5.5.3  | wavelet_controller                                 | 51 |

| 5.5.4  | quantization                                       | 55 |

| 5.5.5  | zle                                                | 57 |

| 5.5.6  | huffman                                            | 60 |

| 5.5.7  | huffman_lookup                                     | 63 |

| 5.5.8  | qzh                                                | 64 |

| 5.5.9  | qzh_controller                                     | 66 |

| 5.5.10 | min_max                                            | 69 |

| 5.5.11 | compare_16b_neg                                    | 70 |

| 5.5.12 | parameter_storage                                  | 71 |

| 5.5.13 | result_params_mux                                  | 72 |

| 5.5.14 | result_controller                                  | 73 |

| 5.5.15 | read_flow_control                                  | 75 |

| 5.5.16 | write_flow_control                                 | 79 |

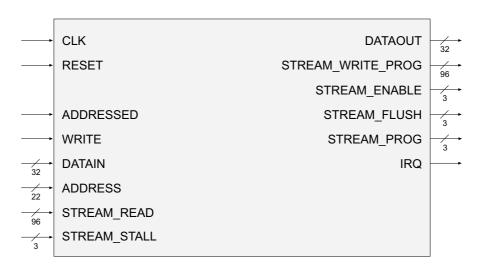

| 5.5.17 | user                                               | 84 |

| 6   | Testumgebung                                                  | 89  |

|-----|---------------------------------------------------------------|-----|

| 6.1 | Funktionen des Testrahmens stimulus                           | 89  |

| 6.2 | Kombinierter HW/SW-Test                                       | 91  |

| 7   | Benchmark-Ergebnisse                                          | 92  |

| 7.1 | Signal- zu Rauschverhältnis und Bits pro Pixel                | 92  |

| 7.2 | Bildvergleiche für unterschiedliche Komprimierungsstärken     | 95  |

| 7.3 | Laufzeit und Fläche                                           | 98  |

| 8   | Zusammenfassung und Ausblick                                  | 100 |

| 9   | Abkürzungsverzeichnis und Begriffserklärungen                 | 102 |

| 10  | Literaturverzeichnis                                          | 104 |

|     | Anhänge auf CD:                                               |     |

| A1  | Anhang 1: optimierter Algorithmus zur Wavelet-Bildkompression |     |

# 1 Einleitung

Adaptive Rechner bieten Geschwindigkeitsvorteile gegenüber Standard-CPUs. Die Hardware eines adaptiven Rechners hat zusätzlich zu einem herkömmlichen Prozessor einen Bereich, in dem sich eine rekonfigurierbare Komponente (engl.: "reconfigurable component" oder kurz "RC") befindet. Dieser Teil der Hardware ist nicht fest bestimmt, sondern kann im laufenden Betrieb geändert werden. So ist es möglich, zeitkritische Berechnungen in Hardware auszulagern, die auf die aktuelle Anwendung maßgeschneidert ist. Anwendungen, die weniger Rechenleistung benötigen (z. B. administrative Aufgaben), können jedoch weiterhin in Software ausgeführt werden. So büßt ein adaptiver Rechner nichts an Flexibilität ein.

Da das Konzept adaptiver Rechner recht neu ist und sich noch in intensiver Forschung befindet, sind bislang vergleichsweise wenige anspruchsvolle Anwendungen auf diesem Gebiet verfügbar. Entsprechend schwierig ist es, aussagekräftige Laufzeit-Vergleichswerte bereitzustellen.

Die Anwendung, die in dieser Studienarbeit auf dem adaptiven Rechner ACE-V entworfen wurde, ist ein Algorithmus zur verlustbehafteten Wavelet-Komprimierung von Graustufenbildern fester Größe. Im Bereich der Wavelet-Komprimierung existiert für adaptive Rechner bislang keine dokumentierte Implementierung, was diese Anwendung sehr interessant macht. Anspruchsvoll ist sie in dem Sinne, dass jeder Eingabedatenstrom in zwei Ausgabeströme resultiert, die in ihrer vollen Länge zwischengespeichert werden, um anschließend erneut als Eingabe zu dienen. Mehrere Berechnungsphasen müssen durchlaufen werden, bevor das Ergebnis vorliegt.

Als Benchmark für adaptive Rechner soll diese Studienarbeit Vergleichswerte für das verwendete System liefern. Dadurch ist es nicht nur möglich, Standardrechner mit adaptiven Rechnern zu vergleichen, sondern auch verschiedene adaptive Rechner untereinander zu messen. Da der C-Quellcode der verwendeten Anwendung frei zugänglich ist, kann dieser Benchmark auch Aussagen treffen über die Effizienz von automatisch generierten Hardwarelösungen. Als Beispiel sei der Compiler NIMBLE [3], [8] genannt, der aus beliebigem C-Code automatisch Soft- und Hardwareteil der Anwendung für einen adaptiven Rechner generiert.

Da für diese Anwendung sehr unterschiedliche und sehr schnelle Speicherzugriffe notwendig sind, wird als Speicherzugriffssystem das in der Abteilung E.I.S. entwickelte System MARC (Memory Architecture for Reconfigurable Computers) [2] eingesetzt.

Nach den in Kapitel 2 beschriebenen Entwurfsvoraussetzungen wird auf den Software-Teil der Anwendung eingegangen (Kapitel 3), danach wird in Kapitel 4 die Hardware-Software-Schnittstelle beschrieben und in Kapitel 5 der Hardware-Teil erläutert. Kapitel 6 fasst wichtige Bemerkungen zur Testumgebung zusammen, bevor Kapitel 7 einige Benchmark-Ergebnisse und Laufzeitvergleiche vorstellt. Eine Zusammenfassung findet sich schließlich in Kapitel 8.

# 2 Anwendung und Entwurfsaspekte

Kapitel 2 enthält einige grundlegende Informationen zur Komprimierung von Bilddaten mittels der diskreten Wavelet-Transformation. Ferner wird der in Software gegebene Algorithmus vorgestellt, der die Grundlage für den Entwurf bildet. Danach werden die Anforderungen an die Studienarbeit definiert, und der letzte Punkt geht auf die Partitionierung der Anwendung in Hardware und Software ein.

#### 2.1 Die diskrete Wavelet-Transformation

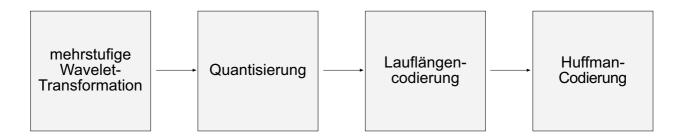

Bild 2.1: Typische Verarbeitungsreihenfolge bei einer Bilddatenkomprimierung mittels Wavelet-Transformation.

Typischerweise geschieht die Wavelet-Komprimierung eines Bildes in vier Phasen (siehe Bild 2.1). Zuerst erfolgt die mehrstufige Wavelet-Transformation der Bilddaten. Hier wird das Ursprungsbild aufgeteilt in einen Datenblock mit etwas vergröberten Bildinformationen und einen anderen Block, in dem die Feinheiten stehen, die bei der Vergröberung im ersten Block verloren gegangen sind. "Mehrstufig" bedeutet, dass dieses Verfahren auf die beiden entstandenen Datenblöcke erneut angewendet wird und so fort.

Die so entstandenen Datenblöcke werden nun der Quantisierung zugeführt. Die Quantisierung hat zwei Aufgaben: einerseits ordnet sie jeweils mehreren Eingabewerten den gleichen Ausgabewert zu (was zu einer kompakteren Zahlendarstellung führt). Andererseits markiert sie Eingaben, die einen besdtimmten Mindestbetrag nicht übersteigen. Interessant ist, dass in dem hier verwendeten Verfahren der Benutzer des Programms die Höhe dieses Mindestbetrages über die Kommandozeile mit der Eingabe der Komprimierungsstärke regeln kann. Je höher die Komprimierungsstärke, um so höher der Mindestbetrag, und damit steigt die Effektivität der Komprimierung; leider aber auch der Qualitätsverlust.

Die nun folgende Lauflängencodierung nutzt Korrelationen zwischen Eingabedaten aus, um verlustfrei zu effizienteren Darstellungen zu gelangen. Das simpelste Beispiel ist, mehrfach hintereinander auftretende Werte zu zählen und als Ergebnis nur die Anzahl dieser gezählten Werte auszugeben. Wie stark ein Datenstrom dadurch komprimiert wird, hängt von der Beschaffenheit der Eingangsdaten ab.

Die so codierten Daten werden zuletzt einer Huffman-Codierung unterzogen. Der Sinn dieser ebenfalls verlustfreien Codierung ist, häufig auftretende Datenworte mit kürzeren Bitfolgen zu codieren als seltener auftretende. So bringt man die gleiche Menge an Informationen in einem kürzeren Ausgabedatenstrom unter.

Die Funktionsweise der vier Phasen soll in den Abschnitten 2.1.1 bis 2.1.4 an Beispielen erläutert werden.

#### 2.1.1 Phase 1: mehrstufige Wavelet-Transformation

Es wurde bereits angedeutet, dass bei der Wavelet-Transformation ein eingehendes Signal in einen Datenblock mit groben Bildinformationen und in einen zweiten mit den dabei verlorengegangenen Feinheiten aufgeteilt wird. Wir betrachten dazu das Beispiel in Bild 2.2.

| Eingangssignal:                  | 13 | 13 | 5 | 5 | 9 | 13 | 21 | 17 |

|----------------------------------|----|----|---|---|---|----|----|----|

| Ausgang 1 (Grobinformationen):   | 1: | 3  | į | 5 | 1 | 1  | 1  | 9  |

| Ausgang 2 (Detailinformationen): | C  | )  | ( | ) | - | 2  | 2  | 2  |

Bild 2.2: Beispiel für die Aufteilung des Eingangssignals in Grob- und Detailinformationen.

Die Grobinformationen (Ausgang 1) des Eingangssignals entsprechen in diesem Beispiel schlicht dem Mittelwert von zwei paarweise aufeinanderfolgenden Eingangsdaten. Ausgang 2 stellt die notwendigen Daten zur Verfügung, um aus den Grob-Informationen das Eingangssignal wieder zurückgewinnen zu können (z. B. ist 11 + (-2) = 9 und 11 - (-2) = 13). Wir bemerken, dass für n Eingangspixel die Ausgänge 1 und 2 je n/2 Ausgangswerte produzieren. Insgesamt bleibt die Datenmenge also gleich.

Man bezeichnet den Datenblock mit Grob-Informationen auch als *Mittelwert-Teil* oder *Low-Pass-Teil* (,,*LP*"), die Detailinformationen nennt man auch *Differenz-Teil* oder *High-Pass-Teil* (,,*HP*"). In Bild 2.2 wurde das einfachste mögliche Beispiel angegeben; die konkrete Berechnungsvorschrift für die Ausgänge 1 und 2 hängt jedoch von der verwendeten Wavelet-Basis ab (siehe z. B. [4]).

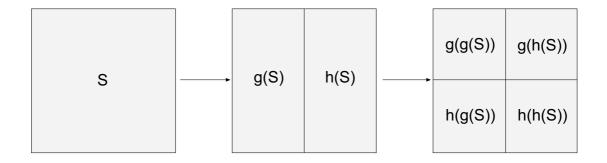

Bild 2.3: Aufteilung des Eingangssignals in Grob- und Detailinformationen.

Allgemeiner entstehen LP und HP durch Anwendung eines LP-Filters g bzw. HP-Filters h auf ein Eingangssignal S, mit nachgeschaltetem Downsampling (die "2" mit dem abwärts zeigenden Pfeil davor), siehe Bild 2.3. Das Downsampling entspricht der oben genannten "paarweisen" Verarbeitung und sorgt dafür, dass LP und HP je halb so lang sind wie das Eingangssignal. Die Rückgewinnung von S geschieht durch Upsampling mit anschließender Anwendung der inversen Filter g' bzw. h', wonach S aus den beiden Teilkomponenten wieder zusammengesetzt werden kann.

Bisher haben wir die Wavelet-Transformation von eindimensionalen Daten beschrieben, ein Bild ist aber zweidimensional. Wie die Transformation eines Bildes gehandhabt wird, zeigt Bild 2.4. In einem ersten Schritt wird jede Bildzeile des Bildes S einzeln einer eindimensionalen Transformation unterworfen, wobei für jede Zeile ein LP-Teil g(S) und ein HP-Teil h(S) anfallen, die jeweils halb so lang wie die Ursprungszeile sind. Unter Beibehaltung der Zeilenreihenfolge werden diese Datenblöcke wie im Bild gezeigt angeordnet g(S) links, h(S) rechts). Das daraus resultierende, zusammengesetzte Bild wird nun erneut transformiert,

Bild 2.4: Wavelet-Transformation auf zweidimensionalen Daten.

diesmal jedoch spaltenweise. Der LP-Teil (g(g(S)) und g(h(S))) wird oben, der HP-Teil (h(g(S))) und h(g(S))) unten angeordnet. Die so entstandenen vier Datenblöcke sind das Ergebnis einer (zweidimensionalen) Transformationsstufe.

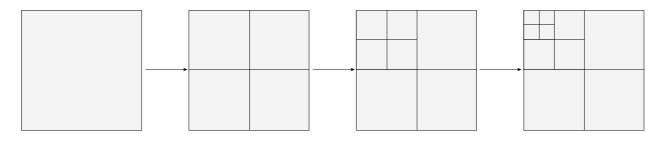

Ziel der Transformation ist es, einen möglichst kleinen Datenblock mit den wichtigsten Bildinformationen zu erhalten neben anderen, größeren Blöcken, die unwichtiger sind und stärker komprimiert werden können. Die "wichtigen" Bildinformationen stecken jeweils in dem LP-Teil der Transformationen. In der zweidimensionalen Betrachtungsweise entspricht dies dem Teil g(g(S)). Man wendet also eine weitere Transformationsstufe auf den Bildausschnitt g(g(S)) an. Man kann nach diesem Schema theoretisch solange fortfahren, bis der finale LP-Teil aus nur noch einem Pixel besteht. In der Praxis erzielt man aber mit vier und mehr Stufen keine weiteren Komprimierungsvorteile mehr, weshalb man meist bei drei Transformationsstufen bleibt. Bild 2.5 zeigt die Verschachtelung der drei Stufen.

Bild 2.5: Verschachtelungs-Schema für drei Wavelet-Transformationsstufen.

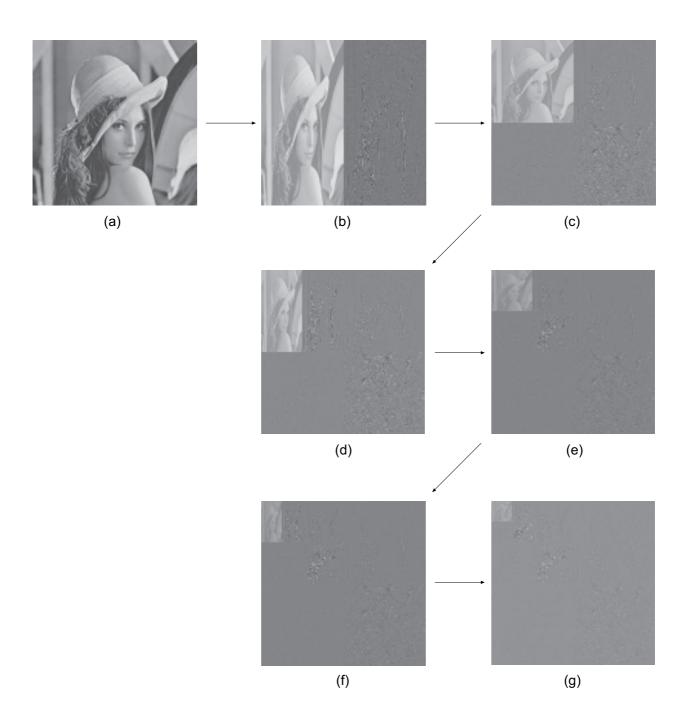

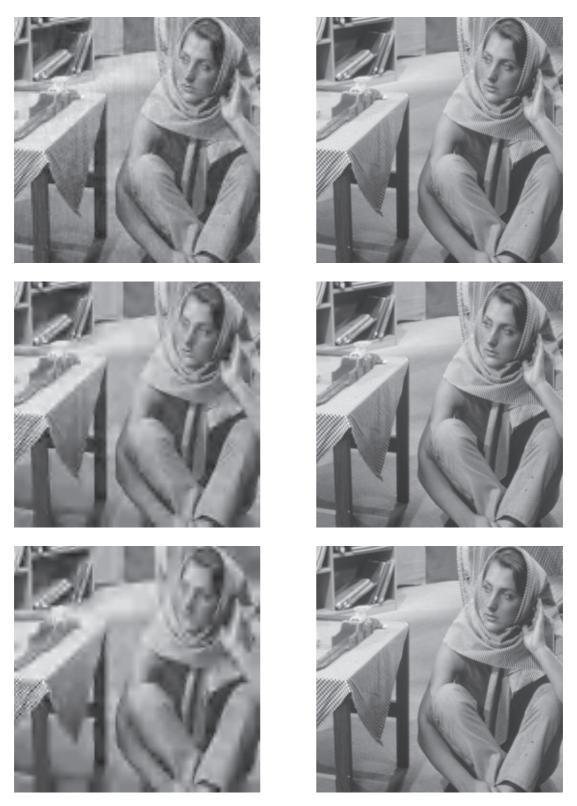

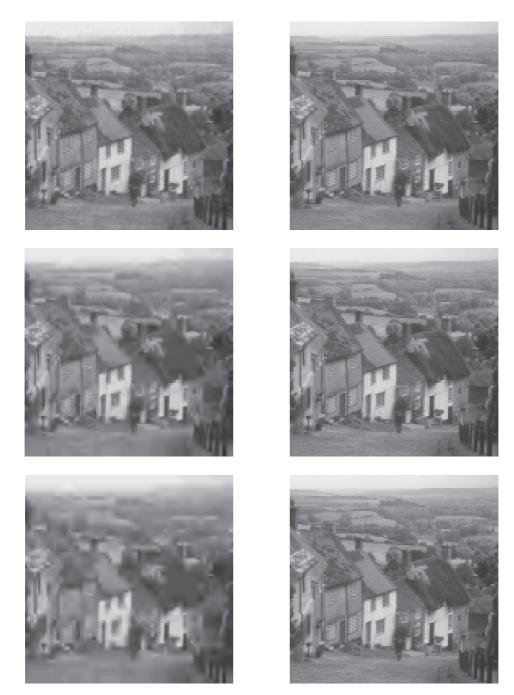

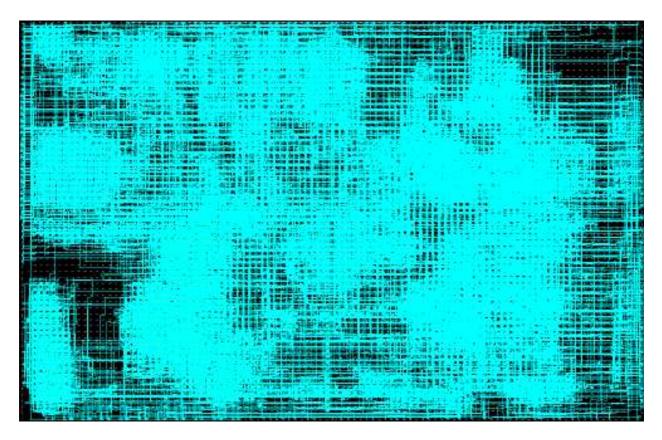

Bild 2.6: Dreistufige Wavelet-Transformation an einem Beispielbild. (a) Originalbild, (b) und (c) Stufe 1, (d) und (e) Stufe 2, (f) und (g) Stufe 3. (g) ist das Ausgabebild der kompletten Wavelet-Transformation.

Um einen Eindruck von den Inhalten der 10 entstandenen Datenblöcke zu erhalten, werfen wir einen Blick auf Bild 2.6. Man erkennt im LP-Teil des Bildes stets das Originalbild wieder; nach der dritten Transformationsstufe ist es nur noch ganz klein oben links zu sehen.

Diese 10 Datenblöcke sind die Eingabe für die nächste globale Bearbeitungsphase: die Quantisierung.

#### 2.1.2 Phase 2: Quantisierung

In der Quantisierung werden jeweils mehrere unterschiedliche Eingabedaten auf das gleiche Ausgabedatum abgebildet. Dadurch ergeben sich weniger mögliche Ausgabewerte, was die Codierung der einzelnen Ausgaben mit weniger Bits gegenüber den Eingaben ermöglicht. Wir betrachten als Beispiel die 6-Bit-Eingabedaten

0 1 5 6 7 35 57 61 62 63

Angenommen, die Quantisierung produziert aus diesen Eingabedaten Ausgabewerte der Länge 4 Bit. Die Werte 0..3 würden dann dem Ausgabewert 0 zugeordnet, 4..7 würden zu 1 codiert usw. Obige Beispielwerte würden zu

0 0 1 1 1 8 14 15 15 15

quantisiert. Es wird unmittelbar klar, dass hier ein Datenverlust auftritt, denn eine Dequantisierung würde

1 1 5 5 5 33 57 61 61 61

ergeben, also lediglich eine Annäherung an die ursprünglichen Daten. Dieser Verlust wird in Kauf genommen.

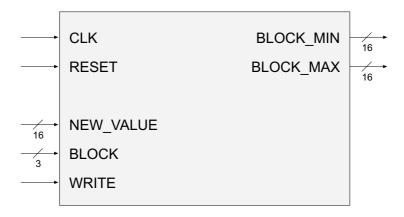

Für eine effiziente Quantisierung müssen das absolute Minimum und Maximum der zu bearbeitenden Daten bekannt sein. Wegen der unterschiedlich gearteten Ausgabeblöcke der Wavelet-Transformation macht es Sinn, jeden Block einzeln zu quantisieren. Die Eingabe für diese Bearbeitungsphase besteht also aus 10 verschieden großen Wavelet-Blöcken mit zugehörigen Block-Minima und -maxmima. Jene Block-Extremwerte werden später zur Dequantisierung gebraucht, und sind daher ein wichtiger Teil der Ergebnisparameter der gesamten Komprimierung.

Die in dieser Studienarbeit verwendete Bearbeitungsreihenfolge der Datenblöcke wird in Bild 2.7 gegeben.

| W0 | W2 | \A/E |      |

|----|----|------|------|

| W1 | W3 | W5   | NA/0 |

| W4 |    | W6   | W8   |

|    | W  | 17   | W9   |

Bild 2.7: Bearbeitungsreihenfolge der Wavelet-Datenblöcke in der Quantisierung.

Eine Besonderheit in der hier verwendeten Methode ist, dass die drei größten Detailblöcke, W7, W8 und W9 (entstanden in Wavelet-Transformationsstufe 1) vernachlässigt, d. h. zu Null gesetzt, werden. Dies macht die Komprimierung sehr viel effektiver, zu einem vergleichsweise geringen Preis in punkto Qualitätsverlust.

Jedem der 7 tatsächlich bearbeiteten Datenblöcke wird ein Block-Grenzwert zugeordnet. Werte, die betragsmäßig kleiner sind als dieser Blockgrenzwert, werden von der Quantisierung besonders markiert

(ein spezieller Ausgabewert dient als Markierung). Dies hat den Zweck, "kleine Details" des Bildes fortzulassen und ermöglicht in der weiteren Verarbeitung eine sehr effiziente Lauflängencodierung. Der Benutzer kann über einen Kommandozeilenparameter die Höhe der Blockgrenzwerte festlegen und so direkt Einfluss nehmen auf die Stärke der Komprimierung und den damit verbundenen Qualitätsverlust.

#### 2.1.3 Phase 3: Lauflängencodierung

In der Quantisierung wurden einige Ausgabedaten speziell markiert. Diese markierten Daten wollen wir im folgenden mit "ZERO" bezeichnen (nicht zu verwechseln mit dem tatsächlichen Wert "0"!). Die Idee der Lauflängencodierung ist, Folgen von gleichen Werten zu erkennen und ihre Länge zu messen. Ausgegeben wird anstatt jedes einzelnen Wertes die Anzahl der direkt aufeinander folgenden Werte. Konzeptionell sollte die Eingabe

erzeugen. Wir bezeichnen hier die "0" als Grundwert und die "5" als Lauflänge. Die Frage ist nun, wie man den Wert "5 mal die 0" im Ausgabestrom codiert. Sicherlich kann man nicht einfach die Ausgaben "5" und "0" schreiben, denn diese Symbole sind bereits für die tatsächlichen Werte 5 und 0 vergeben.

Eine mögliche Codierung besteht darin, einen Teil des Ausgabewortes zur Darstellung des Grundwertes und den anderen Teil zur Lauflängendarstellung zu verwenden. Da die Quantisierung Ausgaben der Breite 4 Bit produziert, würde man dann für eine angenommene Länge der Lauflängen-Ausgabeworte von 8 Bit die ersten 4 Bit zur Grundwertcodierung benutzen und die übrigen 4 Bit zur Lauflängencodierung. Darstellen könnte man damit Läufe bis zur Länge 16.

Um längere Läufe codieren zu können, müsste man weitere Bits spendieren. Man könnte dafür das erste Bit jedes Ausgabewortes als Switch benutzen, um für die aktuelle Ausgabewortlänge von 8 auf 16 Bit umzuschalten oder nicht.

In einem Test zur Evaluierung eines passenden Verfahrens wurden die maximal auftretenden Lauflängengemittelt über die drei Testbilder aus Kapitel 7.2 - gemessen. Legt man die Standard-Komprimierungsstärke 128 zugrunde, ergibt sich für die Eingabewerte 0 bis 15 eine mittlere maximale Lauflänge von 3,25; für die ZERO-Werte jedoch ergab der Test eine mittlere Maximallänge von 762.

Da ZERO-Läufe (bedingt durch die Quantisierung) anscheinend überproportional häufiger auftreten als andere Läufe, ist es insgesamt effizienter, ZERO-Läufe bevorzugt effizient zu codieren. Die in dieser Studienarbeit verwendete Methode ist, nur ZERO-Läufe zu codieren; dadurch spart man nämlich die Codierung der Grundwerte ein. Das Verfahren wird deswegen ab jetzt nicht mehr "Lauflängencodierung", sondern "ZERO-Längencodierung" genannt. Die Tatsächlich verwendete Ausgabewortgröße beträgt 8 Bit, in denen zusätzlich zu den Werten 0 bis 15 die Codes 16 bis 255 für die Codierung der ZERO-Lauflänge verwendet werden.

Als Abkürzung für den Begriff "ZERO-Längencodierung" wird im folgenden häufig "ZLE" verwendet (engl.: "zero length encoding").

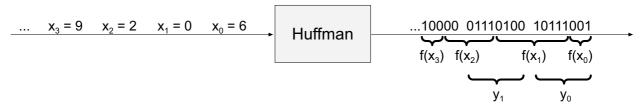

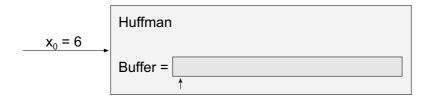

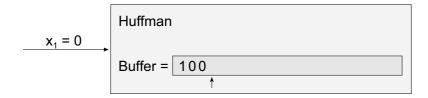

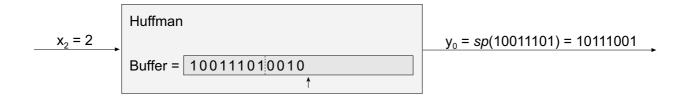

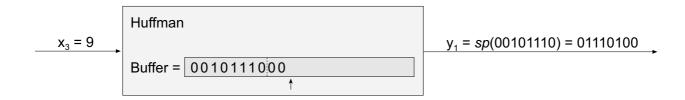

#### 2.1.4 Phase 4: Huffman-Codierung

Die Idee dieser letzten, verlustfreien Komprimierungsphase ist, häufig auftretende Werte mit kurzen Bitfolgen zu codieren, während man für seltener auftretende Werte lange Bitfolgen einsetzt. Angenommen, wir hätten folgenden Datenstrom aus 4 Worten zu je 8 Bit:

| 11110000                                                   | 11110000          | 11110000 | 10100110    | Eingabe       | Ausgabe |  |

|------------------------------------------------------------|-------------------|----------|-------------|---------------|---------|--|

| Mit der Huffman-                                           | -Tabelle in Bild  | :        | :           |               |         |  |

| 0010                                                       | 0010              | 0010     | 01001100111 | 11110000<br>: | 0010    |  |

| Aus 36 Bits wurd                                           | len auf diese Art | 10100110 | 01001100111 |               |         |  |

| Die Implementierung einer Huffman-Codierung wird hardware- |                   |          |             | :             | :       |  |

Die Implementierung einer Huffman-Codierung wird hardwarefreundlicher, wenn die Huffman-Tabelle fest vorgegeben ist, da dann nur ein kompletter Durchlauf durch die Eingabedaten notwendig ist. So wird in dieser Studienarbeit eine feste Tabelle verwendet, die sich für dieses Verfahren bereits bewährt hat.

Bild 2.8: Ausschnitt einer Huffman-Tabelle.

Beliebig geartete Daten mit einer festen Tabelle zu codieren würde natürlich keinen Sinn machen. Wir haben hier aber bereits eine Quantisierung und eine Zerolängencodierung vorgeschaltet, wodurch wir glücklicherweise Aussagen über die Auftrittswahrscheinlichkeit bestimmter Wertebereiche machen können. Die Blockgrenzwerte in der Quantisierung setzen typischerweise entweder sehr wenige aufeinanderfolgende oder alle Werte des aktuellen Blocks zu ZERO. Daher treten für die Huffman-Codierung neben den ohnehin häufigen quantisierten Pixelwerten 0 bis 15 (die von ZLE unangetastet bleiben) noch Eingabewerte von 16 und knapp darüber relativ häufig auf. Je größer die Eingabewerte nun werden, umso unwahrscheinlicher treten sie auf, denn es ist sicher wahrscheinlicher, dass ein Wert zufällig n-mal in Folge als m-mal in Folge auftritt, mit m > n. Eine Ausnahme bildet hier jedoch - wie zuvor angedeutet - der Wert 255. Wurde in der Quantisierung ein ganzer Datenblock mit ZERO markiert, so zählt ZLE entsprechend viele ZERO-Folgen der Länge 255 (längere Folgen werden bei 255 "abgeschnitten", da keine weiteren Bits zur Codierung von größeren Längen zur Verfügung stehen). Diese Überlegungen zu den Auftrittswahrscheinlichkeiten lassen sich anhand der tatsächlich in dieser Arbeit verwendeten Huffman-Tabelle anschaulich nachvollziehen (siehe Anhang 1).

## 2.2 Die Software-Implementierung

Der auf dem adaptiven Rechner ACE-V ([5]) zu entwerfende Algorithmus liegt bereits in Software vor, geschrieben in der Programmiersprache C (siehe [1]). Im Abschnitt 2.2.1 wird die Implementierung des Algorithmus zum besseren Verständnis erläutert. In 2.2.2 sind die Änderungen beschrieben, die an der Software vorgenommen wurden, um sie effizienter und besser hardwarerealisierbar zu machen.

# 2.2.1 Beschreibung der Software-Implementierung

Die Implementierung orientiert sich sehr stark an den in 2.1.1 bis 2.1.4 beschriebenen Bearbeitungsphasen.

Zunächst findet eine Initialisierung (initialize(argc, argv)) statt. Hier werden die Kommandozeilenparameter eingelesen und interpretiert, bestehend aus dem Eingabebild im PGM-Format (siehe z. B. [6]) und der Komprimierungsstärke. Die Komprimierungsstärke ist eine Ganzzahl zwischen 0 und 255. Je größer dieser

Wert ist, umso kleiner wird die komprimierte Datei, umso größer wird aber auch der damit verbundene Qualitätsverlust. Die Komprimierungsstärke legt nämlich die Höhe der Blockgrenzwerte (siehe 2.1.2) fest. Für eine Stärke von 128 (Default-Wert) werden die Blockgrenzwerte  $\{0, 39, 27, 104, 79, 50, 191, 99999, 99999, 99999\}$  verwendet (geordnet nach Blocknummer). Der finale LP-Teil der mehrstufigen Transformation (Block W0) erhält den Grenzwert 0, was dazu führt, dass für beliebige Kompressionsstärken dieser Block immer den Wert 0 zugeteilt bekommt. Die Komprimierungsstärke (gespeichert in der Variablen cratio) skaliert die für den Default-Wert gegebenen Grenzwerte blockthresh nämlich linear:

```

for (i = 0; i < 9; i++)

blockthresh[i] = (blockthresh[i] * cratio) >> 7;

```

Dies ist sehr sinnvoll, da auf diese Weise der LP-Teil (welcher sehr wichtige Informationen hält) keinem zusätzlichen Datenverlust unterworfen wird.

Als nächstes werden in der Methode read\_image(in\_name) die Bilddaten byteweise aus der PGM-Datei eingelesen und in ein Integer-Array kopiert. Die Verwendung des Datentyps Integer ist essentiell, da in der folgenden Wavelet-Transformation die transformierten Werte ein größeres Spektrum einnehmen als die Argumente. 8 Bit pro Wert reichen dafür nicht aus.

forward\_wavelet() führt nun die Wavelet-Transformation durch. Die Schleife

```

\label{eq:for_nt=512;nt} \begin{split} &\text{for (nt=512;nt>=BLOCK\_SIZE;nt>>=1) \{} \\ &\text{for (i=0;i<nt*512;i+=512) fcdf22(&int\_data[i],nt,ROW);} \\ &\text{for (i=0;i<nt;i++) fcdf22(&int\_data[i],nt,COL);} \\ &\} \end{split}

```

ist zwar im Original für die Verarbeitung von 512x512-Pixel-Bildern geschrieben, kann aber leicht verallgemeinert werden für Bilder der Größe  $2^nx2^n$ . Durchlaufen wird die Schleife dann dreimal, was der dreistufigen Transformation entspricht; in jeder Stufe erfolgen zunächst die Zeilen- und anschließend die Spaltentransformationen, jeweils ausgelagert in die Methode fcdf22. In jener Methode halten die Integer-Arrays S[] und d[] die transformierten Werte. S nimmt die Low-Pass-Werte auf, D die High-Pass-Werte.

quantization() ist für die Quantisierung verantwortlich. Die Wavelet-Blöcke werden hier nacheinander durchlaufen. Für jeden Block findet zunächst die Berechnung der Blockminima und -maxima statt, dann folgt die Bestimmung der Quantisierungs-Grenzwerte thresh1 bis thresh16. Falls ein Argument betragsmäßig kleiner als der zu diesem Block gehörige Blockgrenzwert ist (siehe 2.1.2), erfolgt die Markierung mit ,,ZERO\_MARK" (hier wird der Wert 16 für diese Markierung benutzt), ansonsten wird das Argument seinem Quantisierungsbereich zugeordnet (Methode classify(int val)). Die Blockminima und -maxima werden zur späteren Ausgabe nach der Quantisierung des aktuellen Blocks gesichert.

Die Zerolängencodierung RLE\_encode() arbeitet ebenfalls auf jedem Block einzeln. Die einzige hier zunächst nicht sehr anschauliche Quelltextzeile lautet:

```

if ((count == 256 - ZERO_MARK) || (i == img_size)) break;

```

Sie bedeutet, dass die aktuelle Lauflängenzählung beendet wird, wenn der aktuelle Lauf bereits seine maximal erlaubte Länge (siehe 2.1.3) erreicht hat (count == 256 - ZERO\_MARK) oder das Bildende erreicht wurde (i == img\_size).

Die Huffman-Codierung findet in der Methode entropy\_encode() statt; das wesentliche hieran ist die Untermethode hufenc(unsigned char ich, int \*nb). Mit

```

nbits = HufSize[ich];

val = HufVal[ich];

```

wird sowohl die codierte Bitfolge val des Arguments ich in der Huffman-Tabelle HufVal nachgeschlagen

als auch die Länge nbits dieser Bitfolge in der Tabelle HufSize. Wir bemerken, dass hier zwei Tabellen à 256 Einträge nötig sind, die im Programmkopf der Quelltextdatei compress.c definiert wurden. Die Bitfolgen werden dann Bit für Bit dem Ausgabestrom hinzugefügt, wobei dessen aktuelle Bitlänge in nb gesichert wird.

write\_compressed\_file(in\_name) bildet den Abschluss des Verfahrens. Der codierte Bitstrom wird in eine Ausgabedatei geschrieben, mit einem vorangehendem, binärem Header, der wichtige Informationen zur Decodierung beinhaltet. Am Anfang des Headers stehen die Blockminima und -maxima (7 + 7) Integer-Werte), danach folgen die Größen der ZLE-codierten Blöcke (7 Integer-Werte) und in einem letzten Integer-Wert die Länge des codierten Bitstroms in Bytes. Die Headergröße beträgt demnach (7 + 7 + 7 + 1) \* sizeof(int) = 88 Bytes.

# 2.2.2 Effizienzsteigernde Implementierungs-Änderungen

Da die vorgestellte Implementierung sehr verschwenderisch mit Ressourcen umgeht (für die Ausgabe der vier Berechnungsphasen wird jeweils eigener Speicher reserviert), wurde sie vor dem Hardware-Entwurf optimiert (diese Optimierungen sind nicht Teil der Studienarbeit). So wurden die vier Speicherfelder int\_data, quant\_buf, rle\_buf und codep auf die beiden Felder int\_data und quant\_buf reduziert (als ZLE- und Huffman-Ausgaben werden anstatt eigener Speicherbereiche rle\_buf und codep die beiden bereits existierenden Bereiche int\_data und quant\_buf wiederverwendet. Außerdem werden in der optimierten Variante für jeden Zeilen- und Spaltendurchlauf der Wavelet-Transformation nicht zu Beginn die kompletten Daten der Zeile bzw. Spalte einem lokalen Speicher zugewiesen wie dies in der unoptimierten Variante der Fall ist (siehe [1], Methode fcdf22, erste for-Schleife). Stattdessen geschehen diese Zuweisungen direkt während der Berechnungen zur jeweiligen Transformation, so dass hier insgesamt gesehen ein kompletter Bilddurchlauf eingespart wird. Eine weitere Ersparnis besteht in der Verarbeitung der Blökke in Quantisierung und ZLE: da nämlich nur 7 der 10 Wavelet-Blöcke gespeichert werden (die anderen werden zu Null gesetzt), müssen auch nur diese 7 Blöcke anstatt der 10 Blöcke in den beiden Phasen bearbeitet werden.

Eine weitere Optimierung (ebenfalls nicht zu dieser Arbeit gehörig) ermöglicht es der Anwendung, falls sie auf der ACE-V ausgeführt wird, den schnellen SRAM dieser Plattform als Zwischenspeicher für Wavelet-Transformation und Quantisierung zu benutzen.

Zwei kleinere Änderungen wurden im Zuge dieser Arbeit am Algorithmus vorgenommen. In der Quantisierung werden die einzelnen Blöcke im Original spaltenweise durchlaufen:

```

for (i = x; i < x + size; i++) {

for (j = y; j < y + size; j++) {

...

}

}</pre>

```

Für eine hardwareseitige Bearbeitung sind aus Speicherzugriffsgründen zeilenweise Durchläufe effizienter. Deswegen wurden die beiden obigen for-Schleifen vertauscht:

Die nächste und letzte Änderung betrifft die Byte-Länge des Ausgabedatenstroms nach der Huffman-Codierung. Sie wird im Original wie folgt berechnet:

```

nbytes = (nb/8);

```

Dabei ist nbytes die Bytelänge des Ausgabestroms und nb die Anzahl dessen Bits. Da nbytes und nb beides ganzzahlige Werte sind, werden durch diese Zuweisung eventuelle Rest-Bits (maximal 7) vernachlässigt. Diese Vernachlässigung ist aber nicht sinnvoll; also ignoriert die optimierte Software-Fassung jene Bits nicht:

```

nbytes = (nb >> 3);

if (nb % 8!= 0) nbytes++;

```

#### 2.3 Definition der Anforderungen für die Studienarbeit

Aufgabe der Studienarbeit ist es, den gegebenen C-Algorithmus [1] zur wavelet-basierten Kompression von Graustufenbildern in eine kombinierte HW/SW-Lösung für die ACE-V [5] umzusetzen, mit den folgenden Einschränkungen:

- es wird nur die Codierung entworfen, nicht die Decodierung, und

- die Anwendung verarbeitet Bilder der festen Größe 256x256 Pixel, mit 8 Bit Graustufeninformation pro Pixel, im PGM-Format [6].

Dabei sind weitere Anforderungen zu beachten:

- die Komprimierungsstärke soll wie in der Softwarelösung variabel einstellbar sein,

- bei der Ausarbeitung des Entwurfs soll auf möglichst kurze Laufzeiten der Anwendung hingearbeitet werden, und

- wenn die Softwarelösung aus Gründen der effizienteren Hardwarenutzung abgeändert wird, ist zu zeigen, dass die Qualität der erzielten Komprimierung die Versatility-Stressmark-Eigenschaften aufweist (siehe [1]).

Da die ACE-V als Zielplattform ein adaptiver Rechner ist, ist unmittelbar klar, dass die fertige Anwendung aus einem Software- und einem Hardware-Teil besteht. Der Software-Tteil wird in der Programmiersprache C verfasst, der Hardware-Teil in der Hardware-Beschreibungssprache Verilog.

Um das Gros der für die Bearbeitung der Studienarbeit verwendeten Zeit nicht mit der Implementierung von PCI-Kommunikationprotokollen zu verbringen, wird als Speicherzugriffsystem MARC [2] verwendet. MARC bietet sowohl wahlfreie Zugriffe auf einzelne Speicherpositionen als auch Burst-Transfers für die schnelle Übertragung von zusammenhängenden Datenblöcken.

Die Entwicklungsumgebung besteht aus den Programmen "Synplify 7.1.3" (Hardware-Optimierung und Erzeugung der Gatternetzlisten), den Xilinx-Tools in der Version 5.2 (Platzierung, Verdrahtung und Bitstromgenerierung) sowie dem Programm "VCS" von der Firma Synopsys in der Version 6.2 (Simulation).

## 2.4 Partitionierung

Wir wollen nun festlegen, welche Teile des Algorithmus in Hardware ausgelagert werden und welche softwareseitig gerechnet werden.

Wie wir in Abschnitt 2.1 bereits festgestellt haben, besteht die Anwendung im wesentlichen aus den vier

Bearbeitungsphasen der mehrstufigen Wavelet-Transformation, der Quantisierung, Lauflängen- und Huffman-Codierung. Die mehrstufige Wavelet-Transformation beinhaltet sehr viel Arithmetik und sollte deswegen auf jeden Fall in Hardware umgesetzt werden. Die anderen drei Phasen sind effizient zu einer Verarbeitungspipeline hintereinanderschaltbar. Es bietet sich daher an, alle vier Phasen in Hardware auszulagern. Dabei sollte man darauf achten, dass die entworfene Hardware nicht zu kompliziert wird, denn schließlich muss sie in den FPGA der ACE-V passen. Ein Ausweg bei einer zu komplexen Realisierung wäre, die Hardware in mehrere FPGA-Beschreibungen aufzuteilen und den FPGA der ACE-V für jede oder jede zweite Bearbeitungsphase neu zu programmieren. Dies hätte allerdings den Nachteil einer erheblich längeren Laufzeit, da jede Neuprogrammierung und Initialisierung der ACE-V größenordnungsmäßig etwa 2 Sekunden benötigt (das ist um mehrere Größenordnungen mehr, als eine Ausführung des Algorithmus in Software auf einem Standard-PC benötigen würde). Angenehm ist jedoch, dass auf der ACE-V ein sehr großer FPGA steckt (Xilinx Virtex 1000), so dass an Hardware-Komplexität nicht allzu sehr gespart werden muss.

Die Aufgaben des Bilddatenein- und Auslesens von bzw. auf den Festspeicher übernimmt zweckmäßigerweise der Software-Teil der Anwendung.

Übrig bleibt die Berechnung der Blockgrenzwerte:

```

for (i = 1; i < 7; i++)

blockthresh[i] = (blockthresh[i] * quant) >> 7;

```

Diese Berechnung könnte in Hardware ausgeführt werden. Die Vorteile wären, dass die Zeit für die Berechnung in Software (dies sind ca. 5 µs @ 100 MHz CPU-Takt; die auf der ACE-V verwendete CPU ist eine microSPARC IIep) wegfallen würde. Außerdem bräuchte anstatt der sechs Datenworte blockthresh[1], ..., blockthresh[6] nur der Wert quant von der Software in die Hardware übertragen werden. Die Dauer von 6 schreibenden Slave-Mode-Zugriffen liegt derzeit bei ca. 18 µs (bei 30 MHz FPGA-Takt). Das ergäbe eine Ersparnis von maximal 23 µs. Diese Zeit steht in keinem Verhältnis zu der Laufzeit von über 6000 µs, die die Hardware ohnehin für die Abarbeitung der vier Hauptbearbeitungsphasen benötigt (ebenfalls bei 30 MHz FPGA-Takt). Daher wurde die Entscheidung getroffen, die Blockgrenzwertberechnung ebenfalls in Software durchzuführen.

# 3 Der Software-Teil der Anwendung

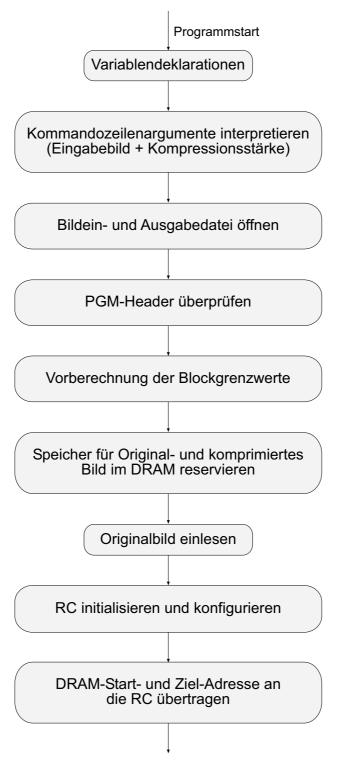

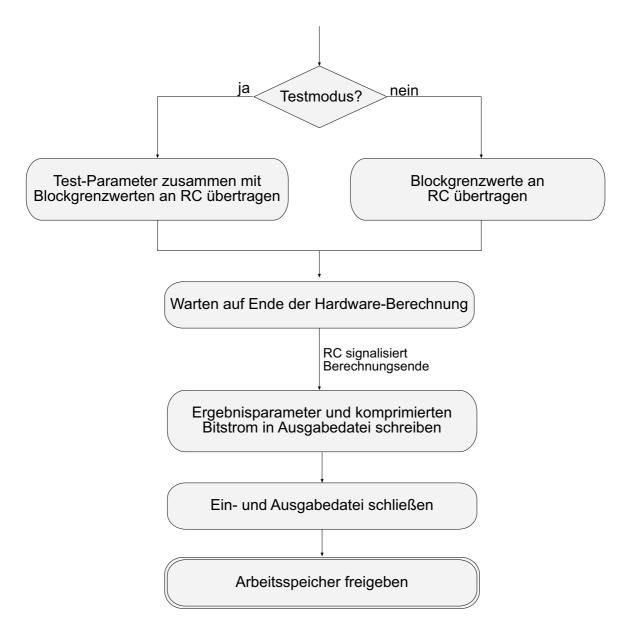

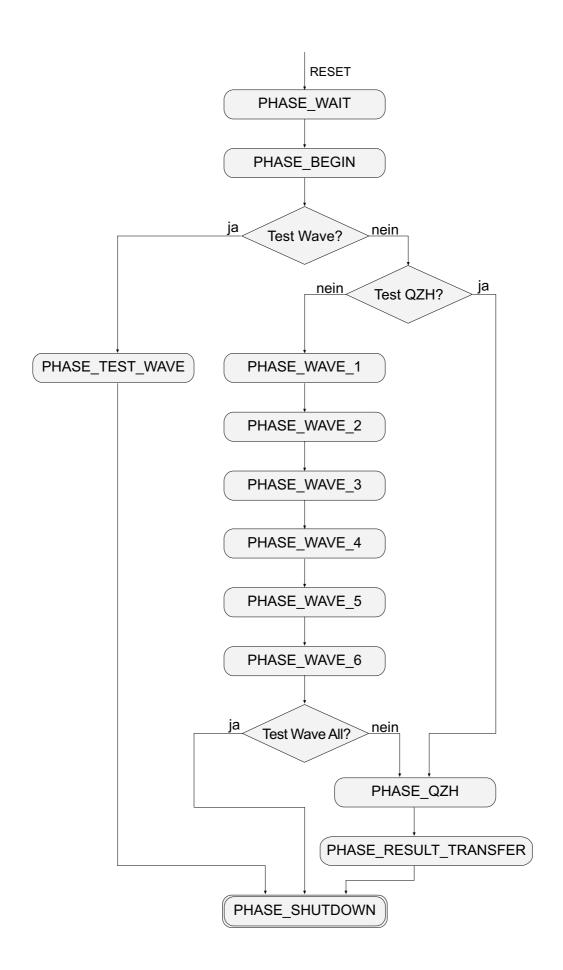

Die Bilder 3.1 und 3.2 geben einen Überblick über den Programmablauf des Software-Teils der Anwendung.

Bild 3.1: Software-Programmablauf, Teil 1 von 2.

Bild 3.2: Software-Programmablauf, Teil 2 von 2.

Die Eingabeparameter (PGM-Bild und Komprimierungsstärke) sind mit denen der reinen Softwarelösung (siehe Abschnitt 2.2) identisch. Dass der Quelltext des Softwareteils der Anwendung hier viel kürzer ausfällt als die reine Softwarelösung ist klar, da ja die meiste Arbeit von der Hardware erledigt wird. Die Software liest lediglich die Bilddaten ein, berechnet die 6 Blockgrenzwerte (der Blockgrenzwert für Wavelet-Block Nr. W0 ist immer 0, daher muss dieser nicht berechnet werden), überträgt einige Parameter an die RC (für eine genauere Beschreibung der Schnittstelle siehe Kapitel 4) und schreibt den komprimierten Bitstrom samt Header in die Ausgabedatei.

Für Laufzeittests ist es wichtig, im Programmkopf die Zeile

#define VERBOSE 1

zu ändern in

#define VERBOSE 0

damit die zu messenden Zeiten nicht durch die zeitintensiven printf()-Aufrufe verfälscht werden.

### Über das Define

#### #define TICKS\_PER\_USEC 30

kann die Taktung der Hardware (in MHz) eingestellt werden. In diesem Beispiel beträgt die Taktung 30 MHz.

Zum Testen einzelner Hardwarekomponenten sowie auch der Hardware als ganzes werden - über Zuweisungen an

### rc[REG\_TESTMODE]

auswählbar - vier verschiedene Testmodi angeboten. Zur Anwendung der Testmodi sei auf Kapitel 6 verwiesen.

### 4 Die Hardware-Software-Schnittstelle

Dank des verwendeten Speicherzugriffsystems MARC [2] konnte der Datenaustausch zwischen Hardund Software-Teil der Anwendung relativ einfach realisiert werden.

### 4.1 Slave-Mode-Zugriffe

Die RC wird in den CPU-Adressraum eingebettet, was lesende und schreibende "memory-mapped"-Speicherzugriffe für den sogenannten Slave-Modus ermöglicht. Dieser Modus wird benutzt, um wie im folgenden Beispiel Parameter von der Software in die Hardware zu übertragen:

```

rc[REG START] = 1;

```

Andersherum kann durch diese simplen Zuweisungen die Software auch Daten von der Hardware lesen, doch lesende Slave-Zugriffe sind sehr zeitintensiv und werden deswegen in dieser Anwendung vermieden.

Der Datentransfer wird für Slave-Mode-Zugriffe von der Software initiiert; die Hardware bleibt dabei also passiv. Den Pointer rc auf den eingebetteten Speicherbereich liefert die in der Datei acevapi.h definierte Methode acev\_get\_s0(NULL). Bei der Definition des Speicher-Pointers rc ist auf die Verwendung des Schlüsselwortes volatile zu achten; nur so wird garantiert, dass der Compiler Zugriffe der Art

```

rc[0] = temp[0];

temp[0] = rc[0];

```

nicht wegoptimiert.

In der Anwendung treten Slave-Mode-Zugriffe lediglich auf, um die Start-Parameter (DRAM-Start- und Ziel-Adresse, Test-Modus-Konfiguration, Hardware-Startsignal) an die RC zu übertragen. Der Rücktransfer der Ergebnisparameter (Blockminima und -maxima, ZLE-Blockgrößen, Huffman-Bytelänge) nach Beendigung der eigentlichen Bilddaten-Transformation geschieht - wie oben bereits erwähnt - aus Effizienzgründen nicht im Slave-Mode.

# 4.2 Master-Mode-Zugriffe

Die zweite mögliche Speicherzugriffsart sind Master-Mode-Zugriffe; die Kontrolle über den Datenaustausch liegt in diesem Fall bei der Hardware. Benutzt werden diese Zugriffe hier zum Lesen und Schreiben der originalen und der transformierten Bilddaten. Die Initialisierung und Übertragung über den ACE-Vinternen PCI-Bus steuert MARC, nachdem für jeden Transfer die Lese- und Schreibströme entsprechend von der Hardware programmiert wurden. Um einen MARC-Strom zu programmieren, müssen die Parameter

- Startadresse,

- Anzahl Datensätze,

- · Schrittweite.

- Wortbreite der Zugriffe sowie

- Zugriffsart (lesen oder schreiben)

eingestellt werden. (Als Beispiel siehe Quelltext z. B. der Datei wavelet\_controller.v.)

Während einer Hardwareberechnung werden in dieser Anwendung typischerweise zwei oder drei MARC-Ströme gleichzeitig benutzt: ein Strom liest Daten ein, ein weiterer schreibt die berechneten Werte an die Zielposition im Speicher. Im Fall der Wavelet-Verarbeitung werden für die Wavelet-Phasen 3 bis 6 (entspricht den Wavelet-Stufen 2 und 3) sogar zwei Schreibströme benötigt: einer für die Low-Daten und einer für die High-Daten.

Abgesehen von gleichzeitig arbeitenden Strömen können MARC-Ströme auch immer wieder neu programmiert werden, um so in verschiedenen Phasen auf unterschiedliche Speicherpositionen zuzugreifen.

Nachdem die Hardware-Berechnung beendet ist, meldet sich die RC bei der Software durch das Setzen eines Interrupts ("IRQ"). Das veranlasst die Software zur Ausführung der Funktion irq\_handler(). Hierin findet ein Slave-Mode-Zugriff auf die RC statt, was den Interrupt (zur weiteren Software-Berechnung) rücksetzt. Anschließend fährt die Software durch den Funktionsaufruf acev\_mark\_done() nach der Stelle acev\_wait() im Hauptprogramm, an der auf das Hardware-Berechnungsende gewartet wurde, fort.

# 5 Der Hardware-Teil der Anwendung

Dieses Kapitel beschreibt die Konfiguration des FPGAs auf der ACE-V für diese Anwendung. Die Hardware muss drei wesentliche Funktionen implementieren: die Entgegennahme von Parametern im Slave-Mode (1), das eigenverantwortliche Transformieren der Bilddaten im Master-Mode (2) sowie die Rück-übermittlung der Ergebnisparameter im Master-Mode (3). Für Punkt (1) sei auf Abschnitt 5.5.17 (detaillierte Beschreibung des Moduls user) verwiesen, da diese Implementierungen sehr kurz und einfach sind. Punkt (3) wird in Abschnitt 5.5.14 (detaillierte Beschreibung des Moduls result\_controller) behandelt. Die Hauptaufgabe der Hardware ist Punkt (2): die Verarbeitung der eigentlichen Bilddaten.

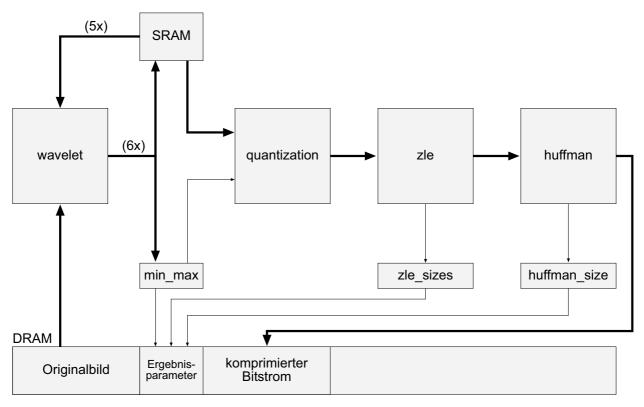

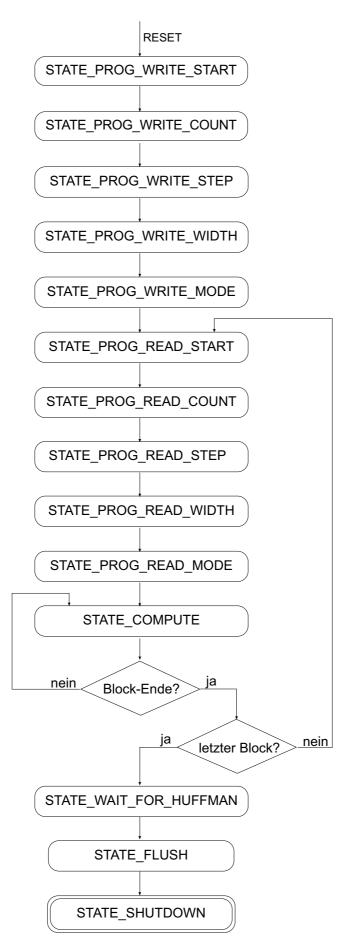

Nach den Vorüberlegungen aus Kapitel 2 lässt sich leicht ein Verarbeitungsablauf definieren; wir werfen dazu einen Blick auf Bild 5.1.

Bild 5.1: Hardware-Verarbeitungsablauf. Die fett gedruckten Pfeile deuten den Weg der Bilddaten an.

Das Originalbild wird aus dem DRAM gelesen, wavelet-transformiert und in den SRAM geschrieben. Da die Transformation dreistufig aufgebaut ist, erfolgen drei Wavelet-Stufen hintereinander, wobei jede Stufe aus zwei Transformationsdurchläufen durch das gesamte Bild besteht: je einmal zeilenweise und einmal spaltenweise. Insgesamt macht das sechs Transformationen, was durch die Beschriftung "6x" im obigen Bild angedeutet wird. Aus dem SRAM müssen die Daten daher fünfmal ("5x") wieder gelesen und der Wavelet-Transformation zugeführt werden (nur für den Zeilendurchlauf der ersten Wavelet-Stufe werden die Daten direkt dem DRAM entnommen; dieser Bereich im DRAM ist mit "Originalbild" gekennzeichnet). Der SRAM ist - ohne Umweg über den internen PCI-Bus der ACE-V - direkt am FPGA angeschlossen und wird daher als schneller Zwischenspeicher in den Wavelet-Stufen gegenüber dem DRAM bevorzugt.

Da die Quantisierung die 7 Blockminima und -maxima benötigt, werden diese in min\_max gespeichert und jeweils während der Wavelet-Transformationen aktualisiert. Die im SRAM abgelegten Wavelet-Blöcke wandern nun der Reihe nach durch die Quantisierung (quantization), die Zerolängencodierung (zle) und

die Huffman-Codierung (huffman) und landen komprimiert im DRAM. Die Ergebnisparameter der ZLE-Blockgrößen sowie die Huffman-Bytelänge werden in zle\_sizes bzw. huffman\_size gespeichert und nach Ende der Bildverarbeitung zusammen mit den Blockminima und -maxima im Master-Mode in den DRAM übertragen.

#### 5.1 Pipelining

Da für die Studienarbeit eine möglichst schnelle Datenverarbeitung eins der Hauptziele ist, wird hier natürlich das bewährte Pipeline-Prinzip eingesetzt. Optimal wäre eine einzige Pipeline, in der alle Transformationsund Komprimierungsschritte enthalten sind. Die Bilddaten würden dann vom DRAM gelesen werden, und am Ende der Pipeline würde der Ergebnisdatenstrom abgegriffen und wieder zurück in den DRAM geschrieben.

Leider kann eine solche Vorgehensweise in dieser Anwendung aber nicht funktionieren. Der Grund ist einfach: die Wavelet-Transformation erfolgt abwechselnd zeilen- und spaltenweise. Bevor die erste Spalte transformiert werden kann, müssen alle ersten Pixel jeder Zeile bereits zeilen-transformiert worden sein. Dies ließe sich durch 256 parallel arbeitende Zeilen-Transformationsmodule erreichen (mit den entsprechenden Speicherzugriffen), was eher illusorisch als praktikabel ist. Praktisch muss ein Zeilen-Transformationsschritt also abgeschlossen sein, bevor die Spaltentransformationen beginnen können. Und genau diese Tatsache verhindert die oben beschriebene Wunsch-Pipeline.

Wir werden Pipelines in der Anwendung also eine Ebene tiefer entwerfen. Ein Zeilen- oder Spaltendurchlauf einer Wavelet-Transformation lässt sich gut pipelinen (Abschnitt 5.1.1). Die drei übrigen Phasen-Quantisierung, Zerolängencodierung, Huffman-Codierung, kurz: "QZH" - lassen sich sogar zu einer größeren Pipeline zusammenfassen (Abschnitt 5.1.2).

## 5.1.1 Wavelet-Pipeline

Da die Wavelet-Transformation Zeile für Zeile bzw. Spalte für Spalte geschieht, ist eine Zeile bzw. Spalte der größte "am Stück" in einer Pipeline bearbeitbare Bereich. Die Tatsache, ob das Bild gerade zeilenoder spaltenweise durchlaufen wird, macht für den Pipeline-Betrieb keinen Unterschied. Anders ist in beiden Fällen jedoch der Gesamtablauf. Bei einer zeilenweisen Bearbeitung können die Daten ohne "Pause" zwischen den Zeilen eingelesen, verarbeitet und ausgegeben werden, im Spaltenfall jedoch muss der Lesestrom nach dem Einlesen einer Spalte erneut programmiert (hier: auf die passende Anfangsposition der nächsten Spalte gesetzt) werden. Eine Spaltenverarbeitungspipeline muss daher während dieser Neuprogrammier-Zeit angehalten werden.

Kurz soll hier noch auf die Wortbreite der verarbeiteten Daten eingegangen werden. Die Original-Bilddaten aus dem DRAM besitzen 8 Bit pro Pixel. MARC kann pro Datenwort maximal 32 Bit liefern, daher ist es für eine schnelle Verarbeitung günstig, jeweils 4 Pixel gleichzeitig einzulesen. Dies geschieht in der Realisierung in der Tat (siehe Modul wavelet\_8\_4\_l, Abschnitt 5.5.1). Ausgegeben werden die transformierten Daten jedoch bereits mit 16 Bit pro Pixel, da pro Wavelet-Transformation - bedingt durch Shifts und Additionen - die Ausgabedaten gegenüber den Eingaben um 1 Bit breiter werden. Ein Bit kommt noch durch die Darstellung im 2er-Komplement für negative Zahlen hinzu (man könnte nach der ersten Transformation 10 Bit, nach der zweiten 11 Bit usw. verwenden, wegen der einfacheren praktischen Umsetzung werden aber auch in diesen Fällen schon 16-bittige Werte benutzt). Ausgegeben werden müssten vom Modul wavelet\_8\_4\_l nun eigentlich 64 Bit (2x 16 Bit Low-Daten + 2x 16 Bit High-Daten), aber glücklicherweise setzt die Quantisierung die drei größten Detailblöcke sowieso zu Null, wodurch hier die

Ausgabe der High-Daten einfach weggelassen werden kann! Die Ausgabe von wavelet\_8\_4\_l besteht daher lediglich aus 2x 16 Bit Low-Daten.

Die übrigen 5 Wavelet-Transformationen (Spaltendurchlauf von Stufe 1 plus Zeilen- und Spaltendurchläufe der Stufen 2 und 3) werden hingegen von wavelet\_16\_2\_hl bewältigt, welches die nun 16 Bit breiten Eingangsdaten mit 2 Pixeln pro Datenwort einliest und entsprechend auch 2x 16 Bit ausgibt; ein Ausgabedatenwort besteht dabei aus einem Low- und einem High-Datum.

Wie die genaue Berechnung in der Wavelet-Transformation lautet und wie diese in einen Pipelinebetrieb umgesetzt wurde, kann man in den detaillierten Modulbeschreibungen der beiden Wavelet-Module wavelet\_8\_4\_l und wavelet\_16\_2\_hl (Abschnitte 5.5.1 und 5.5.2) nachlesen.

#### 5.1.2 QZH-Pipeline

Anders als in der Wavelet-Pipeline erstreckt sich diese Pipeline einerseits über drei verschiedene Module und andererseits über den gesamten Ausgabedatenstrom, bestehend aus 7 Wavelet-Blöcken, die zusammenhängend in einen komprimierten Bitstrom überführt werden.

Im Unterschied zum Wavelet-Fall handelt es sich hier um eine Pipeline mit variabler Datenrate. Das Modul quantization gibt genausoviele Daten aus, wie es einliest. Die beiden Module zle und huffman jedoch machen ihre Ausgabe aber von den eingelesenen Daten abhängig. Wenn zle beispielsweise gerade die Länge eines ZERO-Laufs misst, liest das Modul zwar zu jedem Takt Daten ein, produziert aber keine Ausgabe. Bei huffman kommt noch ein weiterer Punkt hinzu: ist der interne Bit-Puffer zu voll, werden weiterhin Daten ausgegeben, aber im Moment keine eingelesen. Die Module müssen daher selbst kontrollieren können, wann sie Daten lesen, und wann schreiben möchten.

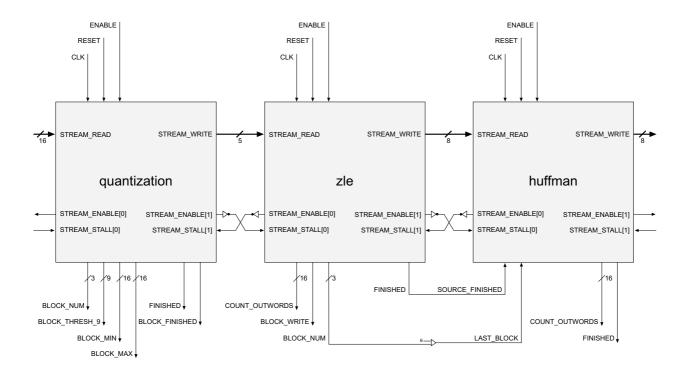

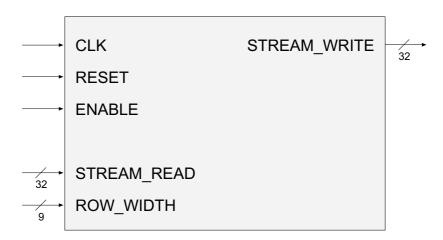

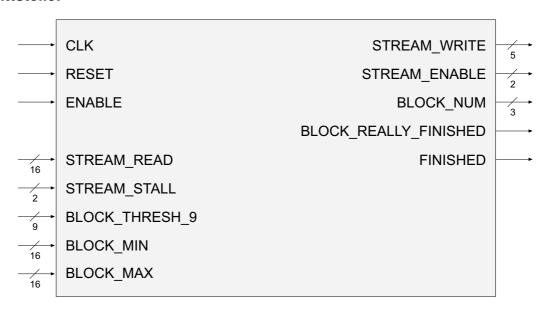

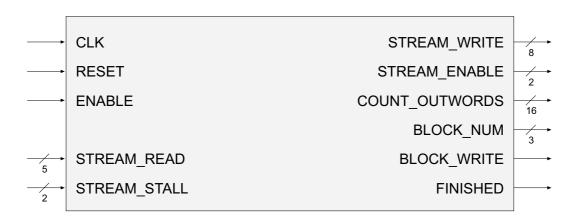

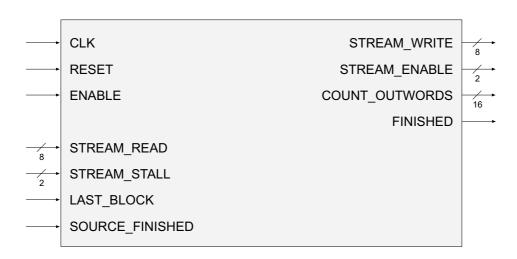

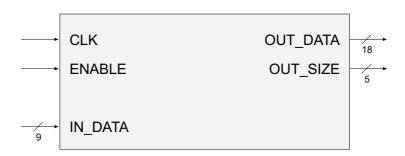

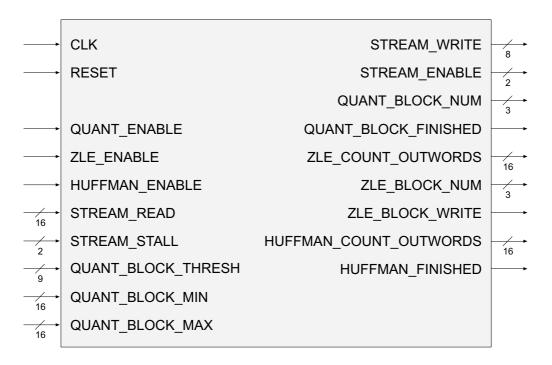

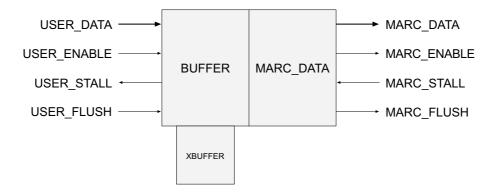

In der Implementierung wurde hier auf das Stream-Konzept gesetzt: Neben einem Datenein- und Ausgangsport (STREAM\_READ und STREAM\_WRITE) hat jedes der drei Module in der QZH-Pipeline einen 2-bittigen "STREAM\_STALL"-Eingang (STREAM\_STALL[0] für den Lesestrom, STREAM\_STALL[1] für den Schreibstrom) sowie entsprechend einen 2-bittigen "STREAM\_ENABLE"-Ausgang. Wenn STREAM\_STALL[0] gesetzt ist, ist das zur aktuellen Taktflanke (dies ist die gerade vergangene Flanke) gelesene Datenwort ungültig und wird nicht verarbeitet. Bei STREAM\_STALL[1] ist das zur aktuellen Taktflanke geschriebene Datenwort ungültig und muss (damit das Datum nicht verlorengeht) erneut an den Ausgang angelegt werden. STREAM\_ENABLE[0] bedeutet, dass das Modul zur aktuellen Taktflanke Daten lesen möchte, STREAM\_ENABLE[1] meint analog, dass zur aktuellen Taktflanke Daten geschrieben werden sollen.

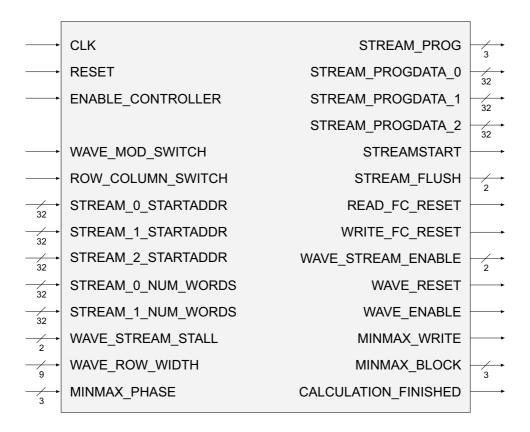

Um das gewünschte Steuerverhalten zu erzielen, werden die Enable-Ausgänge eines Moduls über je einen Inverter mit dem entsprechenden Stall-Eingang der Nachbarmodule verbunden, wie wir es in Bild 5.2 sehen. Mit eingezeichnet sind in diesem Bild auch alle anderen Modul-Ein- und Ausgänge. Die Eingänge CLK, RESET und ENABLE verstehen sich von selbst. Ebenfalls bei allen drei Modulen vorhanden ist der Ausgang FINISHED. Ist FINSHED = 1, so liegt am STREAM\_WRITE-Ausgang des Moduls das letzte gültige Datenwort an.

quantization hat die zusätzlichen Eingänge BLOCK\_THRESH\_9 (Blockgrenzwert des aktuellen Blocks), BLOCK\_MIN und BLOCK\_MAX (aktuelle Block-Minima und -maxima), die zur Quantisierung der Eingangsdaten unerlässlich sind. Zusätzliche Ausgänge sind BLOCK\_NUM und BLOCK\_FINISHED: BLOCK\_NUM gibt die Nummer des Blocks an, aus dem die gelesenen Daten stammen (diese Information ist für die Bereitstellung der korrekten Blockminima, -maxima und -grenzwerte wichtig). BLOCK\_FINISHED hat genau dann den Wert 1, wenn im aktuellen Takt das letzte zu lesende Datum am Dateneingang anliegt (bei BLOCK\_FINISHED = 1 in einem gültigen Lesetakt weiß so der

Bild 5.2: Verkettung der Module quantization, zle, huffman zur QZH-Pipeline. Die fett gedruckten Pfeile deuten den Pfad der komprimierten Bilddaten an.

qzh\_controller, dass er den Lesestrom stoppen kann).

zle hat auch ein BLOCK\_NUM-Signal als Ausgang, das jedoch im Unterschied zum gleichnamigen Quantisierungs-Signal die Blockzugehörigkeit des momentan zu schreibenden Datums angibt, nicht die des zu lesenden Datums. Ist BLOCK\_WRITE = 1, wird die in COUNT\_OUTWORDS gezählte ZLE-Blockgröße des Blocks BLOCK\_NUM von einem außenstehenden Modul zur späteren Abfrage gesichert. Ferner gibt BLOCK\_NUM dem Huffman-Modul die Auskunft, ob es sich momentan um den letzten zu bearbeitenden Block handelt oder nicht. Dazu wird BLOCK\_NUM mit der Zahl 6 verglichen (Block Nr. 6 ist der letzte Block) und - falls die Signale identisch sind - der Eingang LAST\_BLOCK von huffman auf 1 gesetzt.

Falls im Modul huffman die Eingänge SOURCE\_FINISHED und LAST\_BLOCK auf 1 gesetzt sind, weiß das Modul, dass es gerade das letzte gültige Datum liest. Nun muss nur noch der eigene Puffer geleert werden, bevor auch hier FINISHED auf 1 gesetzt werden kann, was dem qzh\_controller das Ende der Berechnung signalisiert.

Der Leser fragt sich nun vielleicht, woher denn quantization und zle die Information über die Blocknummer und die FINISHED-Signale haben, die sie nach außen führen. Da die Anzahl der einzulesenden Datenworte bei beiden Modulen nur von der Größe des Originalbildes abhängt (diese Größe beträgt konstant 256x256 Pixel), zählen beide Module die gültigen Eingabeworte von Anfang an. Es gibt also je ein Zählregister: in quantization heißt es COUNT\_PIXEL, in zle COUNT\_INWORDS. Diese Zählregister werden ständig mit den fest codierten Blockgrößen (Blöcke W0, W1, W2, W3: 1024 Werte; Blöcke W4, W5, W6: 4096 Werte) verglichen, um den Übergang zum nächsten Block festzustellen.

Hinzugefügt sei noch eine Bemerkung zum Modul quantization. Beim Übergang von einem Block zum nächsten müssen die 15 Quantisierungs-Grenzwerte aus dem aktuellen Blockminimum und -maximum berechnet werden, bevor mit der Verarbeitung fortgefahren werden kann. Das Schreib-Stall-Signal muss während dieser Zeit gesetzt sein, um keine ungültigen Daten weiterzugeben.

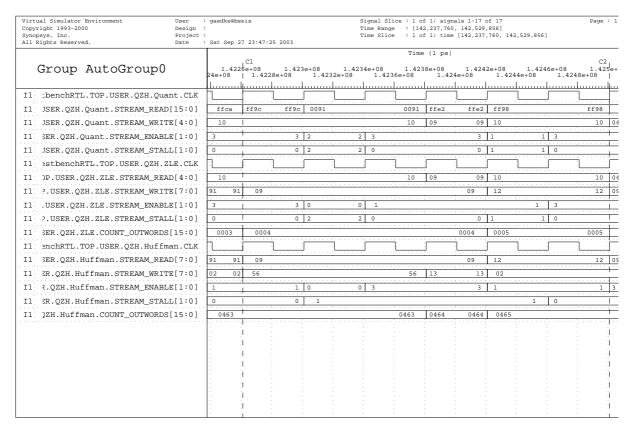

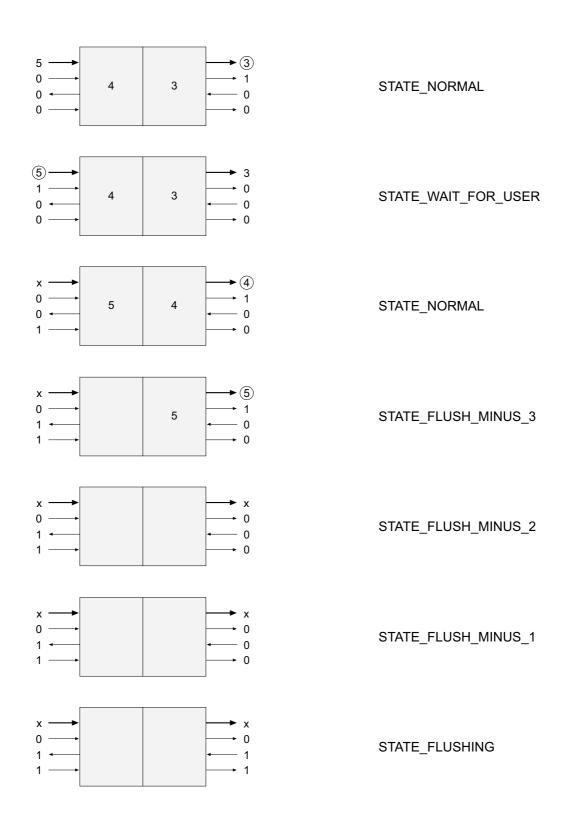

Wir wollen uns nun anhand eines Wave-Diagramms den Weg der wavelet-transformierten Bilddaten durch die QZH-Pipeline anschauen (Bild 5.3).

Bild 5.3: Waveform zur Verarbeitung der wavelet-transformierten Bilddaten in der QZH-Pipeline: oben Quantisierung, mittig Zerolängencodierung, unten Huffman-Codierung.

Der Takt direkt rechts neben der vertikalen gestrichelten Linie "C1" sei Takt Nr. 1, der Takt links neben der Linie "C2" entsprechend Takt Nr. 6. In Takt 1 sehen wir im Signal Quant.STREAM\_READ das Datum, ff9c" (dies ist die Zahl, -100" in hexadezimaler Zweierkomplementdarstellung). Das Wort, ff9c" wird in diesem Takt gelesen, da Quant.STREAM ENABLE[0] = 1 ist (Quant.STREAM ENABLE = 3, d. h. Quant.STREAM\_ENABLE[0] = 1 und Quant.STREAM\_ENABLE[0] = 1) und Quant.STREAM\_STALL[0] = 0. Die "0091", die in Takt 2 am Leseeingang der Quantisierung anliegt, wird jedoch nicht gelesen, da das Lese-Enable (Quant.STREAM\_ENABLE[0]) hier nicht gesetzt ist. Die "ff9c" aus Takt 1 würde in Takt 2 von quantization geschrieben und von zle gelesen, wenn hier nicht Quant.STREAM STALL[1] gesetzt wäre. So wird das Ausgabewort "10", in das die "ff9c" quantisiert wurde, zunächst am Quantisierungs-Ausgang gehalten und erst in Takt 3 von zle gelesen. Das in Takt 3 von der Quantisierung gelesene Wort "0091" wird in den Wert "09" quantisiert, der in Takt 4 von zle aufgenommen wird. zle beendet daraufhin den aktuellen ZERO-Run ("10" = "ZERO"), der bereits drei ZEROs gezählt hat: zwei ZEROs stammen aus der Zeit vor Takt 1, und der dritte ZERO-Wert entstand aus der in Takt 1 von quantization gelesenen Zahl "ff9c". Ein Run, der drei ZEROs gezählt hat, wird mit der Zahl "12" codiert, die tatsächlich in Takt 5 am Ausgang von zle anliegt. Da ZLE.STREAM\_ENABLE[1] jedoch in Takt 5 nicht gesetzt ist, wird die "12" erst in Takt 6 von zle geschrieben und von huffman gelesen. In Bild 5.3 ist noch ansatzweise zu sehen, dass huffman in Takt 7 ein Datum schreibt (Huffman.STREAM\_ENABLE = 3, also lesen und schreiben). Anscheinend hat also der in Takt 6 gelesene Wert "12" den huffman-internen Puffer soweit aufgefüllt, dass ein weiteres Byte geschrieben werden kann. In den Takten 3 und 4 war huffman ebenfalls schreibend aktiv, der Ursprung für jene Ausgaben liegt aber noch vor Takt 1.

Wir bemerken, dass der Byte-Zähler des Huffman-Moduls nach den Takten 3 und 4 jeweils um 1 inkrementiert wird. Das ZLE-Modul dagegen inkrementiert seinen Ausgabewort-Zähler schon zum Schreib-

Takt und nicht erst im Schreib-Takt. Dadurch konnten bereits vorhandene if-Zweige in der Hardware-Beschreibung des Moduls für den Zähler mitverwendet werden, was den Quelltext etwas einfacher macht. Das hat zwar zur Folge, dass z. B. in Takt 5 ZLE.COUNT\_OUTWORDS schon den Ausgabewert 12 gezählt hat, obwohl dieser erst in Takt 6 tatsächlich geschrieben wird. Aber dies hat keine negativen Konsequenzen, da Takt 5 aus Sicht des zle-Moduls wegen des fehlenden STREAM\_ENABLE[1] sowieso kein gültiger Schreibtakt ist.

#### 5.2 Speicherorganisation

Die Aufteilung des DRAM und SRAM in Speicherbereiche ist ein zentraler Aspekt für die Implementierung. Das Speicherzugriffssystem MARC bietet maximal 4 Speicherbereiche an, auf die gleichzeitig zugegriffen werden kann, jeweils entweder lesend oder schreibend. Zunächst sollen die nötigen Speicherblöcke identifiziert werden (5.2.1), danach erfolgt die Aufteilung in die 4 Bereiche für MARC (5.2.2).

### 5.2.1 Speicherzugriffe während der Transformationen

Im QZH-Fall werden die Daten aus den Wavelet-Blöcken nacheinander durch die QZH-Pipeline geschickt und in einen großen Ziel-Bereich im DRAM geschrieben, was relativ unspektakulär ist; daher wird dieser Fall hier nicht extra beleuchtet. Die 6 verschiedenen Wavelet-Phasen (2 Phasen pro Wavelet-Stufe) verlangen aus Sicht der Speicherverwendung aber eine etwas genauere Untersuchung.

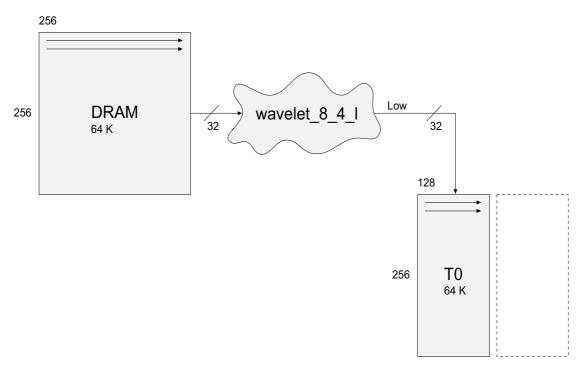

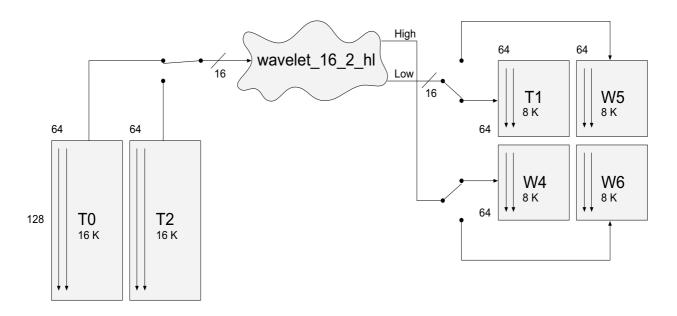

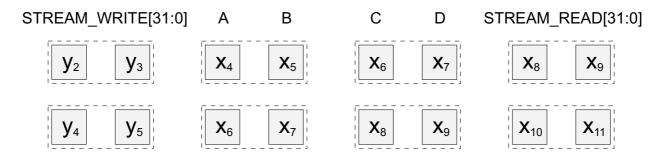

Angegeben werden pro Phase die Speicher- und Datenstrom-Konfiguration. Die identifizierten Speicherbereiche werden mit den Namen W0, W1, W2, W3, W4, W5, W6, T0, T1 und T2 bezeichnet (die allesamt im SRAM liegen). W0 bis W6 stellen die Wavelet-Blöcke dar, die später in der QZH-Pipeline weiterbearbeitet werden, während T0, T1 und T2 nur Zwischenspeicher sind. Die gestrichelten Linien in den folgenden sechs Bildern dienen der Kennzeichnung fortgelassener, nicht gespeicherter Daten. Die Schalter in den Bildern 5.7 und 5.9 werden umgelegt, nachdem die Hälfte der Eingabedaten gelesen bzw. die Hälfte der Ausgabedaten geschrieben wurde. Außerdem wird unterschieden zwischen gleichzeitig geschriebenen Daten ("+" im Text) und sequentiellen Abfolgen (Angabe "danach" im Text; Sequenzen entstehen durch das Umlegen von Schaltern).

Bild 5.4: Speicher- und Datenstrom-Konfiguration, Wavelet-Phase 1.

#### Phase 1 / 6:

Pixelfolge: zeilenweise

Speicherquelle: DRAM (64 K)

Speicherziel: T0 (64 K)

Pixelanordnung Lesen: 256x256

Pixelanordnung Schreiben: 128x256

Wortbreite Lesen: 32 Bit

Wortbreite Schreiben: 32 Bit

Datenformat Lesen: 8 Bit / Pixel, 4 Pixel / Datenwort

Datenformat Schreiben: 16 Bit / Pixel, 2 Pixel / Datenwort (Low-Daten)

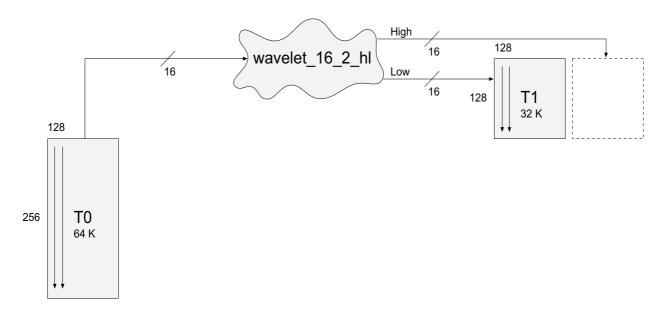

Bild 5.5: Speicher- und Datenstrom-Konfiguration, Wavelet-Phase 2.

#### Phase 2 / 6:

Pixelfolge: spaltenweise

Speicherquelle: T0 (64 K)

Speicherziel: T1 (32 K)

Pixelanordnung Lesen: 128x256

Pixelanordnung Schreiben: 128x128

Wortbreite Lesen: 16 Bit

Wortbreite Schreiben: 16 Bit

Datenformat Lesen: 16 Bit / Pixel, 1 Pixel / Datenwort

Datenformat Schreiben: 16 Bit / Pixel, 1 Pixel / Datenwort (Low-Daten)

In den Phasen 2, 4 und 6 wird pro Takt nur ein Datum eingelesen und wieder geschrieben. In der Spaltenverarbeitung können nämlich mit dem verwendeten Speicherzugriffssystem nicht zwei Pixel gleichzeitig gelesen werden. Man könnte MARC zwar anweisen, 32-Bit-Worte zu lesen anstatt 16-Bit-Worte, würde dann als zweites eingelesenes Datum aber nicht wie gewünscht das zweite Datum der ersten Spalte, sondern das zweite Datum der ersten Zeile erhalten.

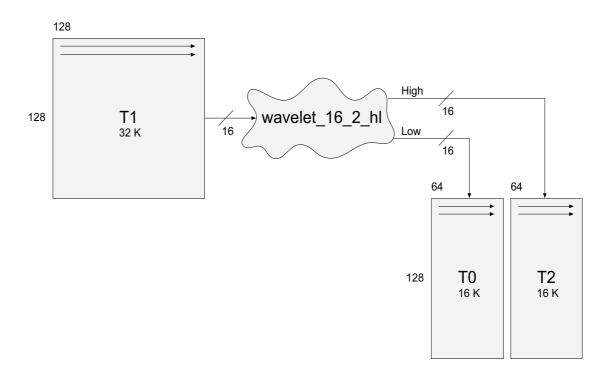

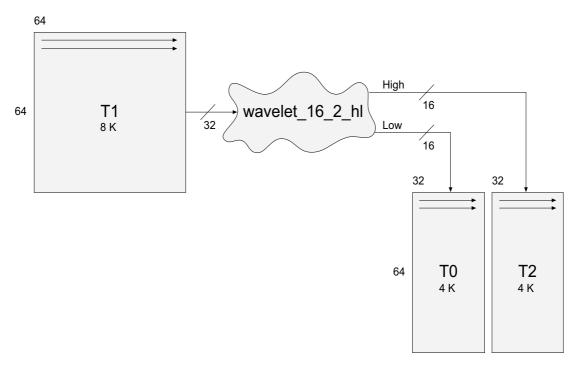

Bild 5.6:

Speicher- und Datenstrom-Konfiguration, Wavelet-Phase 3.

#### Phase 3 / 6:

Pixelfolge: zeilenweise Speicherquelle: T1 (32 K)

Speicherziel: T0 (16 K) + T2 (16 K)

Pixelanordnung Lesen: 128x128

Pixelanordnung Schreiben: 64x128 + 64x128

Wortbreite Lesen: 32 Bit

Wortbreite Schreiben: 16 Bit (Low) + 16 Bit (High)

Datenformat Lesen: 16 Bit/Pixel, 2 Pixel/Datenwort 1 Datenwort/Takt

Datenformat Schreiben: 16 Bit/Pixel, 1 Pixel/Datenwort, 2 Datenworte/Takt

Bild 5.7: Speicher- und Datenstrom-Konfiguration, Wavelet-Phase 4.

#### Phase 4 / 6:

Pixelfolge: spaltenweise

Speicherquelle: T0 (16 K), danach T2 (16 K)

Speicherziel: T1 (8 K) + W4 (8 K), danach W5 (8 K) + 6 (8 K)

Pixelanordnung Lesen: 64x128

Pixelanordnung Schreiben: 64x64 + 64x64

Wortbreite Lesen: 16 Bit Wortbreite Schreiben: 16 Bit

Datenformat Lesen: 16 Bit / Pixel, 1 Pixel / Datenwort

Datenformat Schreiben: 16 Bit / Pixel, 1 Pixel / Datenwort (alternierend 1 Low / 1 High)

Erklärung des Zusatzes "alternierend 1 Low/1 High" unter "Datenformat Schreiben":

Wie schon in Phase 2 beschrieben, kann in der Spaltenverarbeitung nur ein Datum pro Takt gelesen werden. Dies hat zur Folge, dass auch nur eines pro Takt geschrieben werden kann. So werden alternierend Low- und High-Daten geschrieben: im ersten Schreib-Takt wird ein Low-Datum nach T1, im zweiten Takt ein High-Datum nach W4 geschrieben, im dritten Takt das nächste Low-Datum nach T1 usw., bis der Datenblock T0 abgearbeitet ist. Anschließend wird der Inhalt von T2 transformiert und analog nach W5 und W6 geschrieben.

Bild 5.8: Speicher- und Datenstrom-Konfiguration, Wavelet-Phase 5.

#### Phase 5 / 6:

Pixelfolge: zeilenweise Speicherquelle: T1 (8 K)

Speicherziel: T0 (4 K) + T2 (4 K)

Pixelanordnung Lesen: 64x64

Pixelanordnung Schreiben: 32x64 + 32x64

Wortbreite Lesen: 32 Bit

Wortbreite Schreiben: 16 Bit + 16 Bit

Datenformat Lesen: 16 Bit / Pixel, 2 Pixel / Datenwort, 1 Datenwort / Takt

Datenformat Schreiben: 2 Pixel / Datenwort, 2 Datenwort / Takt

(1 Low + 1 High)

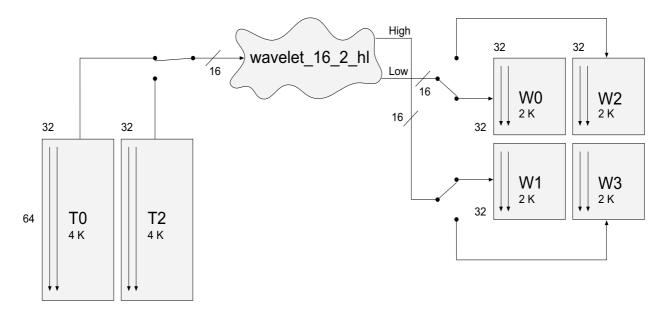

Bild 5.9:

Speicher- und Datenstrom-Konfiguration, Wavelet-Phase 6.

#### Phase 6 / 6:

Pixelfolge: spaltenweise

Speicherquelle: T0 (4 K), danach T2 (4 K)

Speicherziel: W0 (2 K) + W1 (2 K), danach W2 (2 K) + W3 (2 K)

Pixelanordnung Lesen: 32x64

Pixelanordnung Schreiben: 32x32 + 32x32

Wortbreite Lesen: 16 Bit Wortbreite Schreiben: 16 Bit

Datenformat Lesen: 16 Bit / Pixel, 1 Pixel / Datenwort

Datenformat Schreiben: 16 Bit / Pixel, 1 Pixel / Datenwort (alternierend 1 Low / 1 High)

Die Zwischenspeicher T0, T1 und T2 wurden zur effizienteren Speichernutzung während der sechs Phasen mehrfach verwendet. Wir bemerken, dass nicht immer die gleiche Speichermenge für diese Zwischenspeicher verwendet wird; die Dimensionierung muss aber natürlich für den "worst case" ausreichen. Wir erhalten folgende Speichergrößen:

T0: 64 K T1: 32 K T2: 16 K W0: 2 K W1: 2 K W2: 2 K W3: 2 K W4: 8 K W5: 8 K

8 K

W6:

Die Speicherplatznamen W0 bis W6 entsprechen den in Kapitel 2 (Abschnitt 2.1.2) eingeführten Wavelet-Block-Bezeichnungen W0 bis W6.

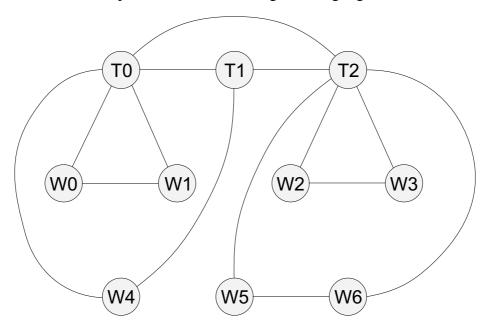

#### 5.2.2 Aufteilung des Speichers für MARC

Optimalerweise würde man die Blöcke W0 bis W6 so im SRAM anordnen, dass die Daten in der QZH-Verarbeitung in einem Rutsch eingelesen werden können, d. h. ohne nach jedem Block die Startadresse des Lesestroms neu zu programmieren. Wir haben wahrgenommen, dass während der Wavelet-Phasen 3 bis 6 auf jeweils drei Speicherblöcke gleichzeitig zugegriffen wird (1x lesend, 2x schreibend). Die MARC-Philosophie besagt nun, dass solche gleichzeitig bearbeiteten SRAM-Blöcke in unterschiedlichen Speicherbereichen liegen müssen. Insgesamt sind aber maximal vier solcher Bereiche erlaubt. Es stellt sich also die Frage, ob die 10 Blöcke so in 4 Bereiche einsortiert werden können, dass einerseits keine zwei gleichzeitig bearbeiteten Blöcke in ein und demselben Bereich liegen und andererseits die optimale Speicheranordnung "W0 bis W6" eingehalten werden kann.

Die Blöcke, auf die gleichzeitig zugegriffen wird, lauten:

(T0, T1, T2), (T0, T1, W4), (T2, W5, W6), (T0, W0, W1), (T2, W2, W3).

Blöcke, die in einer Gruppe liegen, dürfen nicht im selben MARC-Speicherbereich angesiedelt sein. Dieses Problem lässt sich als graphentheoretische Fragestellung formulieren:

Gegeben sei ein ungerichteter Graph G mit der Knotenmenge  $V = \{W0, W1, W2, W3, W4, W5, W6, T0, T1, T2\}$  und der Kantenmenge  $K = \{\{W0, W1\}, \{W0, T0\}, \{W1, T0\}, \{W2, W3\}, \{W2, T2\}, \{W3, T2\}, \{W4, T0\}, \{W4, T1\}, \{W5, W6\}, \{W5, T2\}, \{W6, T2\}, \{T0, T1\}, \{T0, T2\}, \{T1, T2\}\}.$

Die Knoten entsprechen dabei den 10 Datenblöcken. Zwischen zwei Knoten existiert eine Kante genau dann, wenn MARC auf die entsprechenden Datenblöcke gleichzeitig zugreift.

Bild 5.10: Graph G; Knoten = Speicherblöcke, Kanten = gleichzeitiger Zugriff.

Wir suchen eine Aufteilung der Knoten in 4 Teilmengen, wobei zwischen Knoten aus unterschiedlichen Teilmengen keine Kante verlaufen darf.

Unter Einhaltung der Reihenfolge "W0 bis W6" ergäben sich unter Beachtung der Restriktionen durch den Graphen die Speicherbereiche (W0), (W1, W2), (W3, W4, W5), (W6). Die drei Blöcke T0, T1, T2 können nur an zwei Stellen in die Sortierung eingefügt werden (Anfang oder Ende), da sonst die Reihenfolge W0, …, W6 unterbrochen werden würde. Nach dem Schubfachprinzip werden zwei der drei Blöcke am Anfang oder am Ende eingefügt. Dies ist aber verboten, da die drei Blöcke im Graphen eine Clique bilden und deswegen zwingend drei unterschiedlichen Speicherbereichen zugewiesen werden müssen.

Man muss also eine andere Aufteilung wählen. Tatsächlich verwendet wird in der Implementierung die folgende (Bezeichnungen A, B, C, D für die vier MARC-Speicherbereiche):

Es fällt auf, dass die Bereiche stets etwas größer gewählt wurden als nötig. Dies geschah lediglich, um die

Bild 5.11:

Tatsächliche Einteilung der 10 Blöcke in die 4 möglichen MARC-SRAM-Speicherbereiche.

Konfiguration des MARC-Kerns zu vereinfachen. Der DRAM liegt als zusätzlicher Bereich unterhalb der eingebetteten SRAM-Bereiche. Die genaue Adressierung sieht wie folgt aus:

```

24'h000000 ... 24'hFBFFF DRAM via PCI (16MB-256KB)

24'hFC0000 ... 24'hFDFFF SRAM A (128 KB)

24'hFE0000 ... 24'hFEFFFF SRAM B (64 KB)

24'hFF0000 ... 24'hFF7FFF SRAM C (32 KB)

24'hFF8000 ... 24'hFFFFFF SRAM D (32 KB)

```

Dadurch lauten die Adressbereiche der einzelnen Blöcke:

W0 = 24'hFE0000 ... 24'hFE07FF W1 = 24'hFF0000 ... 24'hFF07FF W2 = 24'hFF8000 ... 24'hFF87FF W3 = 24'hFE0800 ... 24'hFE0FFF W4 = 24'hFF0800 ... 24'hFF27FF W5 = 24'hFF8800 ... 24'hFFA7FF W6 = 24'hFE1000 ... 24'hFE2FFF T0 = 24'hFC0000 ... 24'hFDFFFF T1 = 24'hFE3000 ... 24'hFEAFFF T2 = 24'hFF2800 ... 24'hFF67FF

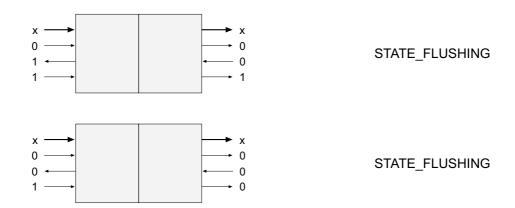

### 5.3 Stream-Flusskontrolle

Im Abschnitt 5.1.2 über das QZH-Pipelining haben wir bereits eine Idee davon bekommen, wie eine Flusskontrolle funktioniert. Nach demselben Prinzip wird auch der Datenfluss an der MARC-Schnittstelle im Master-Mode gesteuert.

Für den Fall zweier gleichzeitig arbeitender Ströme, ein Lese- und ein Schreibstrom, betrachten wir die MARC-Steuer- und Datensignale und ihre Bedeutung.

#### Lesestrom:

STREAM\_ENABLE[0]:

Ist STREAM\_ENABLE[0] gesetzt, liegen zur nächsten Flanke an STREAM\_READ gültige Daten zum Lesen an, aber nur, falls momentan (seit der vergangenen Flanke) STREAM\_STALL[0] nicht gesetzt ist. Ist STREAM\_ENABLE[0] nicht gesetzt, liegen zur nächsten Flanke an STREAM\_READ keine gültigen Daten an.

• STREAM\_STALL[0]:

Ist STREAM\_STALL[0] gesetzt, liegen zur nächsten Flanke keine gültigen Daten an.

• STREAM\_READ:

Lese-Datenport.

### Schreibstrom:

STREAM\_ENABLE[1]:

Ist STREAM\_ENABLE[1] gesetzt, liegen momentan (seit der vergangenen Flanke) an STREAM\_WRITE\_PROG gültige Daten zum Schreiben an, aber nur falls momentan (seit der vergangenen Flanke) STREAM\_STALL[1] nicht gesetzt ist. Ist STREAM\_ENABLE[1] nicht gesetzt, liegen momentan (seit der vergangenen Flanke) an STREAM\_WRITE\_PROG keine gültigen Daten zum Schreiben an.

STREAM\_STALL[1]:

Ist STREAM\_STALL[1] gesetzt, liegen momentan (seit der letzten Flanke) keine gültigen Daten zum Schreiben an.

• STREAM WRITE PROG:

Schreib-Datenport.

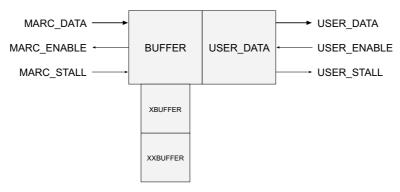

Die Schaltung dieser Studienarbeit lässt sich intuitiver programmieren und einfacher debuggen, wenn sich die Signale Stall und Enable des Lesestroms - genau wie beim Schreibstrom auch - auf den aktuellen Takt (die vergangene Flanke) beziehen. Das Modul read\_flow\_control ist gerade für diese Übersetzungen entworfen worden. Es dient aber auch zur Verzögerung der Signale, die die Grenze zwischen MARC und der Schaltung passieren, um kritische Pfade zu verkürzen. Analog befindet sich zwischen je einem der beiden Schreibports der Schaltung und dem zugehörigen MARC-Port eine Instanz des Moduls write\_flow\_control.

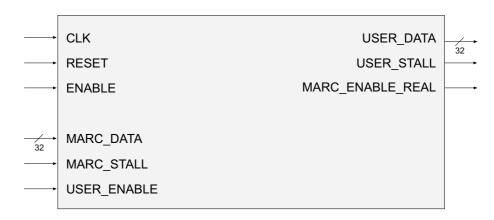

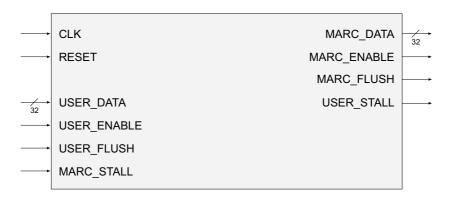

read\_flow\_control und write\_flow\_control betreiben demnach keine Datenverarbeitung im eigentlichen Sinn. Sie sind lediglich für die Weiterleitung von Signalen zu den jeweils korrekten Zeitpunkten zuständig. Um dies deutlich zu machen, unterscheiden sich die Stream-Schnittstellen der Flusskontroll-Module von denen der QZH-Module. Z. B. hat quantization die Ausgänge STREAM\_ENABLE[0] für den Lesestrom und STREAM\_ENABLE[1] für den Schreibstrom sowie die Eingänge STREAM\_STALL[0] des Lesestroms und STREAM\_STALL[1] des Schreibstroms. read\_flow\_control hat hingegen auf der Leseseite (MARC) den Eingang MARC\_STALL und den

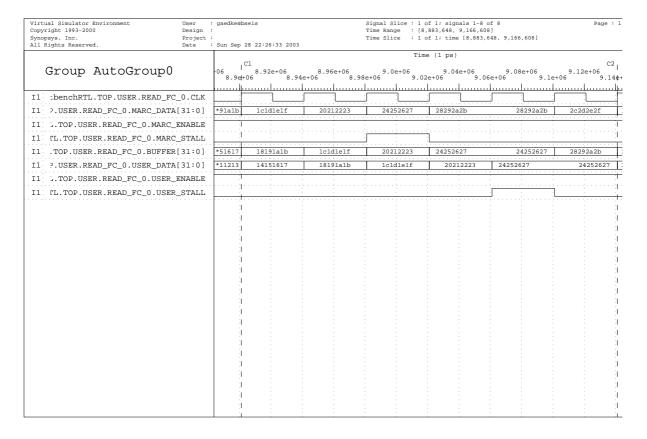

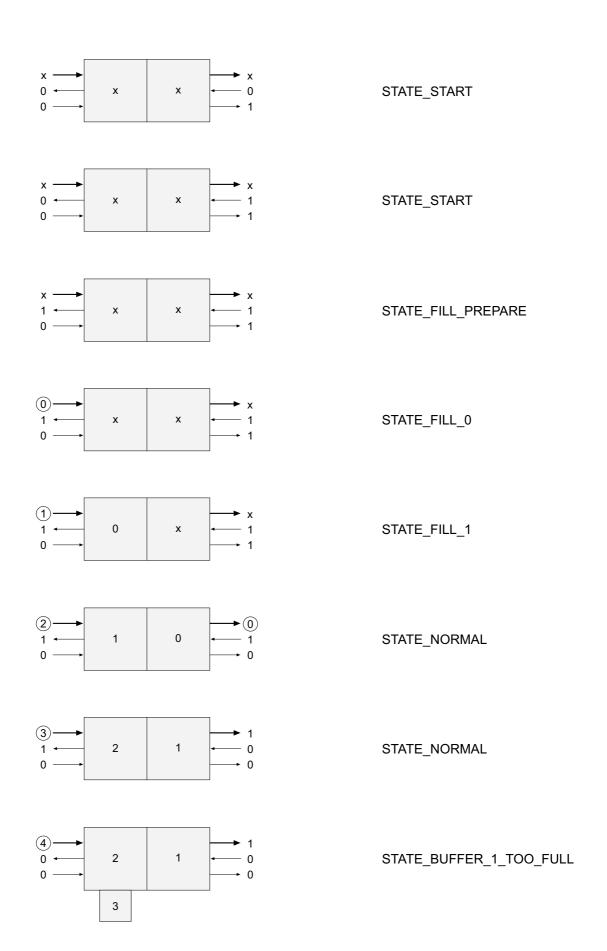

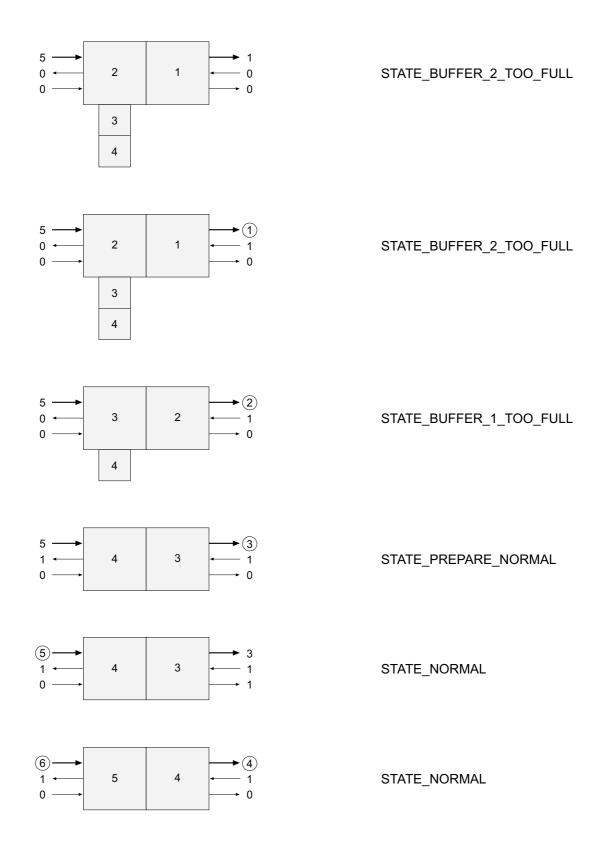

Bild 5.12: Eine RTL-Simulationsausgabe für das Modul read\_flow\_control.

Ausgang MARC\_ENABLE, und auf der Schreibseite (user) den Eingang USER\_ENABLE und den Ausgang USER\_STALL.

In Bild 5.12 sehen wir eine Simulationsausgabe des Moduls read\_flow\_control als Waveform. Der oberste Signalverlauf gibt den Takt wieder. Die drei direkt darunter liegenden Signale MARC\_DATA, MARC\_ENABLE und MARC\_STALL sind Signale der MARC-Schnittstelle, der fünfte Signalverlauf stellt den Inhalt des Puffers innerhalb read\_flow\_control dar, und die untersten drei Signale sind die entsprechenden Daten- Enable- und Stall-Signale der user-Schaltung. Wir nummerieren in Gedanken die Takte zwischen den vertikalen gestrichelten Begrenzungslinien mit den Nummern 1 bis 6 durch. Der Stall des MARC-Stroms in Takt 3 bedeutet, dass das Datum "28292a2b" in Takt 4 ungültig ist. Es wird daher zum Takt 5 nicht in den modulinternen Puffer geschrieben. In Takt 4 schreibt read\_flow\_control das noch im Puffer gehaltene Datum "20212223" und meldet der user-Schaltung erst in Takt 5 einen Stall, um den Puffer zum Takt 6 hin wieder mit einem neuen Datum zu füllen.

Hervorgehoben sei anhand des Bildes die unterschiedliche Bedeutung der Stall-Signale: MARC meldet in Takt 3 einen Stall und sagt damit aus, dass das in Takt 4 anliegende Datum "28292a2b" ungültig ist. read\_flow\_control gibt der user-Schaltung in Takt 5 einen Stall und meint damit, dass das in Takt 5 anliegende Datum "24252627" ungültig ist.

Um die Schaltung für eine höhere Taktung zu entwerfen, war es nötig, einige kritische Pfade zu verkürzen. Die längsten Pfade verliefen von der Anwendung über die Flusskontrolle zu MARC und wieder zurück in die Anwendung. Ein idealer Punkt für eine Pfadaufspaltung war daher die Flusskontrolle selbst, und zwar im Lese- wie im Schreibfall. In read\_flow\_control und write\_flow\_control wurde also eine Verzögerungsstufe zur Pfadverkürzung eingearbeitet.

# 5.4 Der Hardware-Teil im Überblick

Um nicht nur Detaileinblicke wie in Abschnitt 5.5 zu geben, wird die Hardware hier global beschrieben. So bekommt der Leser einen Überblick über die verschiedenen Modulinstanzen und deren Zusammenwirken.

Zunächst nennen wir alle zur Anwendung gehörenden Module bzw. Modulinstanzen (Module ohne eigenen Instanznamen wurden je nur einmal instanziert):

- wavelet\_8\_4\_I

- wavelet\_16\_2\_hl

- wavelet\_controller

- quantization

- zle

- huffman

- huffman\_lookup

- qzh\_controller

- qzh

- min\_max

- compare\_16b\_neg

- parameter\_storage, Instanz Blockthresh)

- parameter\_storage, Instanz ZLE\_sizes)

- result\_params\_mux

- result\_controller

- read\_flow\_control

- write\_flow\_control, Instanz WRITE\_FC\_1

- write\_flow\_control, Instanz WRITE\_FC\_2

- user

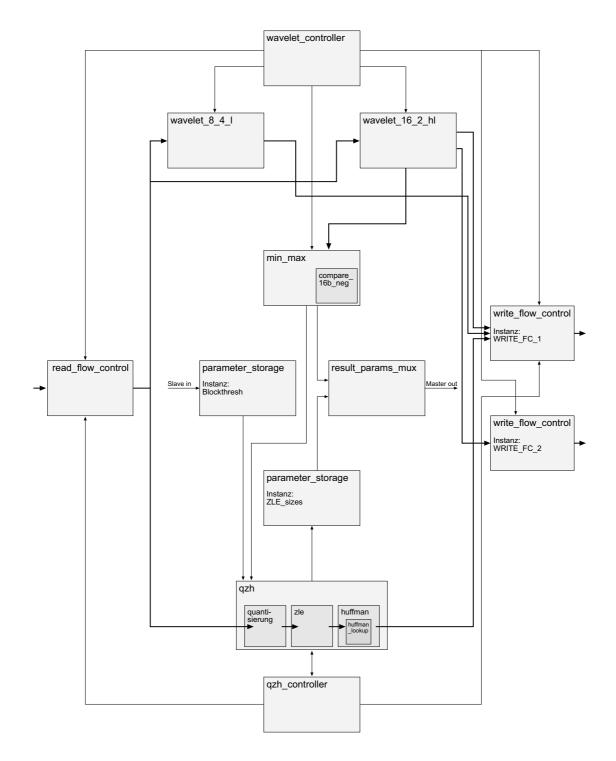

Alle diese Module sind in Bild 5.13 aufgeführt, mit Ausnahme des Moduls result\_controller (mehr dazu weiter unten). Das user-Modul ist der globale Rahmen der Anwendung; im Bild wurde er der Übersichtlichkeit halber weggelassen.

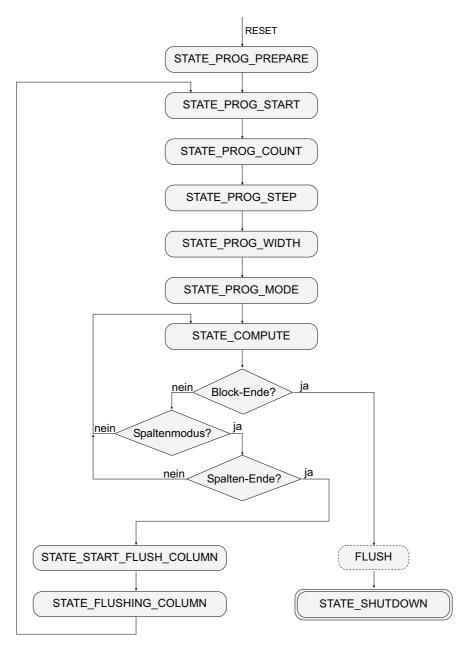

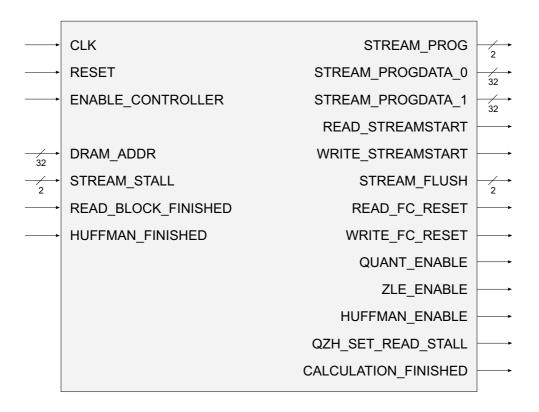

Oben in Bild 5.13 ist der Wavelet-Bereich angesiedelt. Je nach Phase wird wavelet\_8\_4\_l oder wavelet\_16\_2\_hl zur Berechnung verwendet. wavelet\_controller ist für die Programmierung der Ströme (Streams) zuständig und darf die Flusskontroll-Module read\_flow\_control und write\_flow\_control rücksetzen. Zusätzlich steuert dieser Controller die Aktualisierung der Blockminima und -maxima in min\_max.

Nach Abschluss der Wavelet-Phasen wird qzh\_controller aktiv, der die Programmierung der Streams übernimmt. Der zweite Schreibstrom (Zugriff über write\_flow\_control, Instanz WRITE\_FC\_2) wird hierbei im Gegensatz zur Wavelet-Verarbeitung nicht verwendet.

qzh beinhaltet die zur QZH-Pipeline nötigen Modulinstanzen quantization, zle und huffman, die nun die Eingangsdaten in den Ausgabe-Bitstrom umwandeln. Da die QZH-Module für sich selbst feststellen, welcher Block gerade verarbeitet wird und wann die Berechnung beendet ist, werden diese Informationen an den Controller übermittelt, der so vorhandene Ressourcen nutzen kann. Trotzdem behält der Controller insofern die Kontrolle über den QZH-Ablauf, als dass er die gesamte Pipeline anhalten kann, um den Lesestrom zu Anfang jedes Blockes auf die korrekte Startadresse einzustellen.

Wie schon angedeutet bietet read\_flow\_control zusammen mit den beiden write\_flow\_control-Instanzen

Bild 5.13: Überblick über den gesamten Hardware-Teil der Anwendung. Fette Linien deuten die Wege der Bilddaten an. Aus Gründen der Übersichtlichkeit wurde das Modul result\_controller hier ausgelassen.

die Schnittstelle zu den drei MARC-Strömen an. MARC-Streams werden traditionell durchnummeriert; Stream 0 wird hier nur als Lesestrom genutzt, die Streams 1 und 2 stellen die beiden über die write\_flow-control-Instanzen WRITE\_FC\_1 und WRITE\_FC\_2 ansprechbaren Schreibströme dar. Der zweite Schreibstrom wird lediglich während den Wavelet-Phasen verwendet, und selbst dann nur in den Phasen 3 bis 6, wenn tatsächlich High-Daten geschrieben werden.

Die vier in der Mitte des Bildes befindlichen Modulinstanzen dienen der Speicherung und Ausgabe der Ergebnisparameter. parameter\_storage wird zweimal instanziert: Blockthresh speichert die im Slave-Mode von der Software übertragenen Blockgrenzwerte, ZLE\_sizes nimmt die 7 ZLE-Blockgrößen und

auch die Huffman-Bytelänge auf. min\_max hält die während der Wavelet-Verarbeitung aktualisierten Blockminima und -maxima, die zur QZH-Phase dem Modul qzh zugänglich gemacht werden. Für eine geordnete Ausgabe der Ergebnisparameter sorgt das Modul result\_params\_mux. Nachdem die QZH-Phase beendet ist, steuert das Modul result\_controller das Kopieren der Ergebnisparameter in den DRAM im Master-Mode (benutzt wird Schreibstrom 1). Da diese Übertragung kein wesentlicher Teil der eigentlichen Datentransformationen ist, wurde result\_controller im Schaubild 5.13 fortgelassen; so ist das Bild auch übersichtlicher.

# 5.5 Detaillierte Modulbeschreibungen

# 5.5.1 wavelet\_8\_4 I

# **Funktionsbeschreibung:**

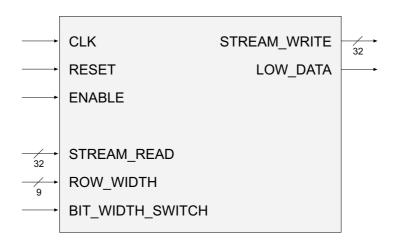

wavelet\_8\_4\_list ein Modul zur Durchführung einer Wavelet-Transformation nach dem (2, 2)-biorthogonal-Cohen-Daubechies-Fouveau-Verfahren [7]. Es werden dabei lediglich ganzzahlige Werte verwendet. Pro Takt wird ein 32-Bit-Datenwort (4 Bildpixel zu je 8 Bit) gelesen; geschrieben werden nur die Low-Daten der Transformation, daher nur 2 transformierte Werte pro Takt, jedoch zu je 16 Bit. So haben Dateneingangs- und Ausgangsport (STREAM\_READ und STREAM\_WRITE) je 32 Bit.

Der Name "wavelet\_8\_4\_1" bedeutet, dass jedes eingelesene Bildpixel 8 Bit breit ist, und dass 4 Pixel pro Takt (zusammengefasst in einem 32-Bit-Datenwort) eingelesen werden. Das "l" steht für "low": es werden nur die Low-Daten der Berechnung ausgegeben.

#### Schnittstelle:

| CLK          | Globale Clock.                                                                                                        |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------|--|

| RESET        | Reset-Signal, getrieben von wavelet_controller.                                                                       |  |

| ENABLE       | Enable-Signal, getrieben von wavelet_controller.                                                                      |  |

| STREAM_READ  | Dateneingangssignal, von user getrieben. Das erste Datenwort besteht aus den Bits 31:24, das vierte aus den Bits 7:0. |  |

| ROW_WIDTH    | Gibt die Länge der Zeilen des zu bearbeitenden Bildes an; getrieben von wavelet_controller.                           |  |

| STREAM_WRITE | Datenausgangssignal. Das erste Datenwort besteht aus den Bits 31:16, das zweite aus den Bits 15:0.                    |  |

### Implementierung:

Um eine möglichst effiziente Datenverarbeitung zu gewährleisten, wendet dieses Modul das Pipelining-Prinzip an. Die Daten werden von STREAM\_READ in einen Puffer kopiert, dort transformiert und nach STREAM\_WRITE geschrieben. Als Puffer wären theoretisch 4 mal 8 Bit (entsprechend einem Takt) ausreichend; jedoch wird hier ein weiterer Takt gepuffert, um einen kritischen Pfad in der Schaltung zu verkürzen. Schematisch lässt sich die Pipeline wie folgt darstellen:

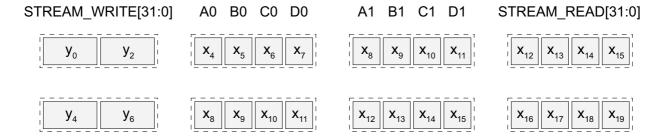

STREAM\_WRITE <= {A0, B0, C0, D0} <= {A1, B1, C1, D1} <= STREAM\_READ

- Takt 1: Kopieren der Eingangsdaten von STREAM\_READ nach {A1, B1, C1, D1}.

- Takt 2: Kopieren der Daten von {A1, B1, C1, D1} nach {A0, B0, C0, D0}.

- Takt 3: Transformation (verwendet zur Berechnung A0, B0, C0, D0, A1 und einen weiteren Wert XB, der weiter unten erläutert wird) sowie Schreiben der Ergebnisse nach STREAM\_WRITE.

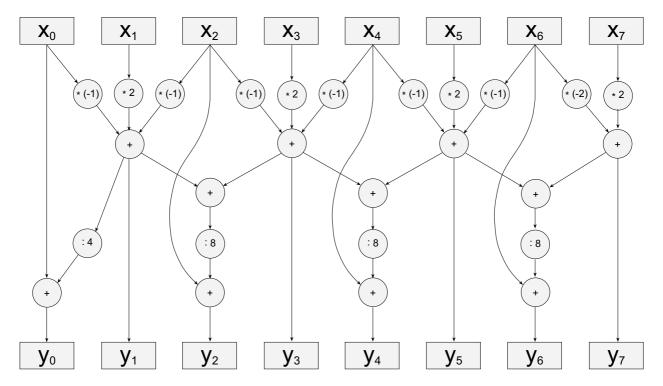

Um die Wavelet-Transformation, die das Modul durchführt, nachvollziehen zu können, wirft man zunächst einen Blick auf folgendes Datenflussdiagramm:

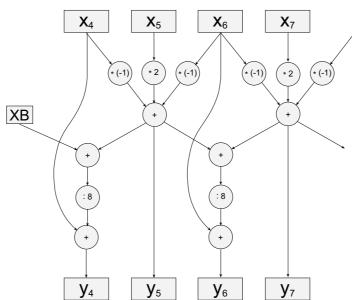

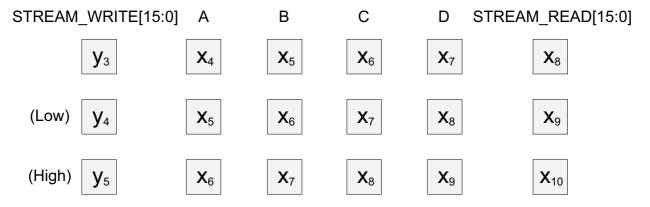

Bild 5.14: Datenflussdiagramm für die Transformation einer 8 Pixel breiten Bildzeile  $[x_0, ..., x_7]$  in Low-Pass-Daten  $[y_0, y_2, y_4, y_6]$  und High-Pass-Daten  $[y_1, y_3, y_5, y_7]$ . Als Basisfunktionen werden (2, 2)-biorthogonale Cohen-Daubechies-Fouveau-Wavelets verwendet.

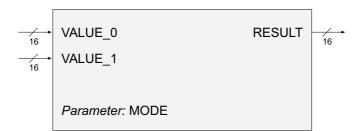

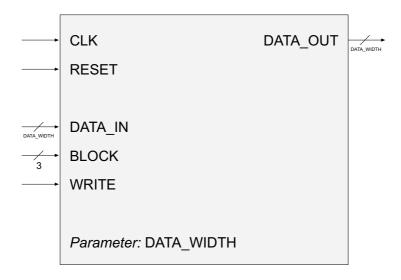

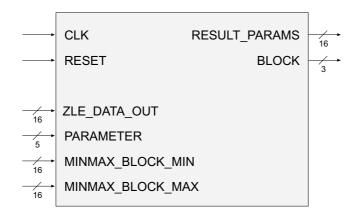

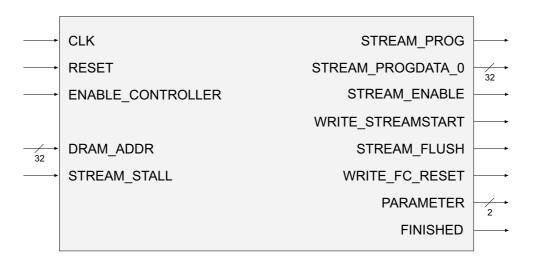

Dieses Diagramm erklärt die Berechnungen, die für die verlangte Wavelet-Transformation durchgeführt werden müssen, wobei hier eine Zeilenlänge von 8 Pixeln beispielhaft zugrundegelegt wird. (Die Berechnung lässt sich aber sehr leicht auf n Pixel erweitern, mit n gerade.) Die Eingangsdaten sind hier  $x_0, x_1, ..., x_7$ , die entsprechenden Ausgangsdaten sind  $y_0, y_1, ..., y_7$ . Der "Low"-Bereich der komprimierten Bildzeile wäre in diesem Fall  $\{y_0, y_2, y_4, y_6\}$ , der "High"-Bereich entsprechend  $\{y_1, y_3, y_5, y_7\}$ . Man sieht deutlich, dass am Zeilenanfang  $(x_0)$  und -ende  $(x_7)$  die Berechnung anders ist als im restlichen Teil der Zeile. Daher benötigt die berechnende Einheit als Parameter stets die Zeilenlänge.